CN1556976A - 显示装置及其驱动方法 - Google Patents

显示装置及其驱动方法 Download PDFInfo

- Publication number

- CN1556976A CN1556976A CNA028184742A CN02818474A CN1556976A CN 1556976 A CN1556976 A CN 1556976A CN A028184742 A CNA028184742 A CN A028184742A CN 02818474 A CN02818474 A CN 02818474A CN 1556976 A CN1556976 A CN 1556976A

- Authority

- CN

- China

- Prior art keywords

- current

- transistor

- pixel

- electric current

- current source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/36—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators characterised by the display of a graphic pattern, e.g. using an all-points-addressable [APA] memory

- G09G5/39—Control of the bit-mapped memory

- G09G5/399—Control of the bit-mapped memory using two or more bit-mapped memories, the operations of which are switched in time, e.g. ping-pong buffers

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3283—Details of drivers for data electrodes in which the data driver supplies a variable data current for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/003—Details of a display terminal, the details relating to the control arrangement of the display terminal and to the interfaces thereto

- G09G5/006—Details of the interface to the display terminal

- G09G5/008—Clock recovery

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/18—Use of a frame buffer in a display terminal, inclusive of the display panel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

Abstract

显示装置的各个像素分别具有电流源电路、开关部和发光元件。在电源基准线和电源线间串联连接发光元件、电流源电路和开关部。通过使用数字图像信号,而切换开关部的接通断开。另外,由从像素外部输入的控制信号确定在电流源电路中流过的一定电流的大小。在开关部为开状态的情况下,在发光元件中流过由电流源电路确定的一定电流而发光。结果,提供一种显示装置及其驱动方法,可以以一定亮度使发光元件发光,而与由劣化等造成的电流特性的变化无关,且将信号写入到各像素的写入速度提高,也可表现正确的灰度等级,低成本、可以小型化。

Description

技术领域

本发明涉及显示装置及其驱动方法。尤其有关对每个像素设置晶体管,来控制像素发光的有源矩阵型显示装置及其驱动方法。

背景技术

已经公开了对每个像素配置发光元件和控制发光元件发光的晶体管的有源矩阵型显示装置。所谓发光元件,是指具有第一电极和第二电极,并通过在第一电极和第二电极间流过的电流量控制亮度的元件。瞩目于使用OLED(OrganicEmitting Diode)元件作为发光元件的显示装置(下面,记为OLED显示装置)。由于OLED显示装置具有响应性好,能在低电压下操作,并且视野角度宽等优点,所以作为下一代平板显示器备受关注。

在有源矩阵型OLED显示装置中,存在由电压信号向各像素写入亮度信息的方法和由电流信号写入的方法。将前一方法称为电压写入型,将后一方法称为电流写入型模拟方式。下面,举例说明这些驱动方法。

图30表示现有的电压写入型OLED显示装置的像素的构成例。在图30中,分别对各像素配置两个TFT(第一TFT和第二TFT)、电容元件和OLED。将第一TFT(下面,记为选择TFT)3001的栅极与栅极信号线3002相连,将源极端子和漏极端子的一个端子与源极信号线3003相连。将选择TFT3001的源极端子与漏极端子的另一个与第二TFT(下面,记为驱动TFT)3004的栅极和电容元件(下面记为保持电容)3007的一个电极相连。将保持电容3007的另一电极与电源线3005相连。将驱动TFT3004的源极端子和漏极端子的一个与电源线3005相连,另一个与OLED3006的第一电极3006e相连。将规定电位施加给OLED3006的电极3006b。这里,将OLED3006的与驱动TFT3004相连侧的电极,即第一电极3006a称为像素电极,将第二电极3006b称为对置电极。

在图30中,下面,说明选择TFT3001为n沟道型TFT,驱动TFT3004为p沟道型TFT,OLED的第一电极3006a为阳极,第二电极3006b为阴极,第二电极3006b的电位为0(V)时的驱动方法。

在将信号输入到栅极信号线3002,为导通状态的选择TFT3001中,从源极信号线3003输入信号电压。通过输入到源极信号线3003的信号电压,而将电荷贮存到保持电容3007中。根据在保持电容3007中保持的电压,从电源线3005经驱动TFT3004的源和漏极间而在OLED3006中流过电流而发光。

在具有图30所示结构的像素的电压写入型显示装置中,存在模拟方式和数字方式两种驱动方法。下面,将这两种方式称为电压写入型模拟方式、电压写入型数字方式。

在电压写入型模式方式的驱动方法中,通过使各像素的驱动TFT3004的栅极电压(栅极和源极间电压)变换,而改变驱动TFT3004的漏极电流。这样,为改变在OLED3006中流过的电流而改变亮度的方法。为了表现中间色调,对于栅极电压,使驱动TFT3004在漏极电流变化大的区域中动作。

在上述电压写入型模拟方式中,在从源极信号线3003对各像素输入具有相同电位的信号时,存在因驱动TFT3004的电流特性的偏差而因为漏极电流的改变,在OLED3006中流过的电流有很大偏差的问题。驱动TFT3004的电流特性的偏差受阈值电压和载流子迁移率等参数影响。作为其中的一例,使用图31,说明因驱动TFT3004的阈值电压偏差引起的电流特性的偏差。

图31(A)是仅表示图30的驱动TFT3004和OLED3006的图。将驱动TFT3004的源极端子与电源线3005相连。图中由Vgs表示驱动TFT3004的栅极电压。另外,图中由箭头Id表示驱动TFT3004的漏极电流。图31(B)表示驱动TFT3004的栅极电压的绝对值|Vgs|与漏极电流Id的关系(电流特性)。3101a是表示驱动TFT3004的阈值电压的绝对值为Vth1的情况下,栅极电压与漏极电流的关系的曲线。另一方面,3101b是表示驱动TFT的阈值电压绝对值为Vth2的情况下,栅极电压与漏极电流的关系曲线。这里,Vth1>Vth2。图中所示的动作区域(1)相当于电压写入型模拟方式情况下驱动TFT3004的动作区域。在动作区域(1)中,若驱动TFT3004的阈值有偏差,即使栅极电压相同为Vgs1,但漏极电流为Id1和Id2,而有很大不同。这里,由于OLED3006的亮度与在OLED3006中流过的电流量成正比,所以因阈值电压有偏差,OLED3006的亮度有偏差。

为了降低上述驱动TFT3004的电流特性的偏差影响,提出了电压写入型数字方式的驱动方法。在电压写入型数字方式的驱动方法中,各像素的OLED3006选择在一定亮度下发光/非发光两种状态。这时,图30的驱动TFT3004工作为选择各像素的电源线3005和OLED3006的像素电极3006a连接的开关。在电压写入型数字方式中,在OLED3006发光时,驱动TFT3004在栅和漏极间电压Vds的绝对值比栅极电压Vgs减去阈值电压Vth的电压Vgs-Vth的绝对值小的动作区域的线性区域,尤其是在栅极电压的绝对值大的区域中动作。

图31(B)中,由动作区域(2)表示在电压写入型数字方式下的驱动TFT3004的动作区域。动作区域(2)是线性区域,在该区域中动作的驱动TFT3004在施加了同一栅极电压Vgs2的情况下,因阈值电压等的偏差而造成的漏极电流的偏差减小,而流过大致一定的电流Id3。因此,可以抑制在OLED3006中流过的电流偏差,抑制发光亮度的变化。

使用图32说明分别对在线性区域动作的驱动TFT3004和OLED3006所施加的电压的关系。为进行说明,图32(A)是仅示出图30的驱动TFT3004和OLED3006的图。这里,将驱动TFT3004的源极端子与电源线3005相连。由Vds表示驱动TFT3004的源极和漏极间电压。由VOLED表示OLED3006的阴极和阳极间的电压。由IOLED表示在OLED3006中流过的电流。电流IOLED等于驱动TFT3004的漏极电流Id。由Vdd表示电源线3005的电位。将OLED3006的对置电极的电位设为OV。图32(B)中,3202a是表示OLED3006的VOLED和IOLED的关系(I-V特性)的曲线。另外,3201是图31(B)的栅极电压为Vgs2情况下驱动TFT3004的源和漏极间电压Vds与漏极电流Id(IOLED)的关系曲线。由两个曲线的交点决定驱动TFT3004和O

LED3006的动作条件(动作点)。另外,由于驱动TFT3004在线性区域动作,所以图中所示的线性区域中的曲线3201和曲线3202a的交点3203a为动作点。即,将OLED3006的阳极和阴极间的电压设为VA1,将电流设为IOLED1。

另一方面,在具有电流写入型模拟方式的像素的显示装置中,从信号线(源极信号线)对各个像素输入信号电流。这里,信号电流是线性的对应于视频信号的亮度信息的电流信号。将所输入的信号电流作为漏极电流的TFT的栅极电压保持在电容部中。这样,在不再从源极信号线向像素输入信号电流后,还在OLED上持续流过由电容部存储的电流。这样,通过改变输入到源极信号线的信号电流而改变在OLED中流过的电流,控制OLED的发光亮度而表现灰度等级。

作为电流写入型模拟方式的像素例子,在图33中表示“IDW`00p235:ActiveMatrix PolyLED Displays”所公开的像素结构,并说明其驱动方法。在图33中,由OLED3306、选择TFT3301、驱动TFT3303、电容元件(保持电容)3305、保持TFT3302、发光TFT3304、源极信号线3307、第一栅极信号线3308、第二栅极信号线3309、第三栅极信号线3310、电源线3311构成像素。

将选择TFT3301的栅极电极与第一栅极信号线3308相连。将选择TFT3301的源极端子和漏极端子一个与源极信号线3307相连,另一个与驱动TFT3303的源极端子或漏极端子、保持TFT3302的源极端子或漏极端子和发光TFT3304的源极端子或漏极端子相连。通过保持TFT3302的源极端子和漏极端子将没有与选择TFT3301相连的一侧与保持电容3305的一个电极和驱动TFT3303的栅极相连。将保持电容3005的没有与保持TFT3302相连的一侧与电源线3311相连。将保持TFT3302的栅极与第二栅极信号线3309相连。通过驱动TFT3303的源极端子和漏极端子将没有与选择TFT3301相连的一侧与电源线3311相连。通过发光TFT3304的源极端子和漏极端子将没有与选择TFT3301相连一侧与OLED3306的一个电极3306a相连。将发光TFT3304的栅极与第三栅极信号线3310相连。将OLED3306的另一电极3306b保持在一定电位上。另外,将OLED3306的两个电极3306a和3306b中,没有与发光TFT3304相连一侧的电极3306a称为像素电极,将另一个电极3306b称为对置电极。

在图33所示结构的像素中,构成为由视频信号输入电流源3312控制输入到源极信号线的信号电流的电流值。另外,实际上,对应于多个像素列的多个视频信号输入电流源3312相当于源极信号线驱动电路的一部分。这里,以选择TFT3301、保持TFT3302和发光TFT3304为n沟道型TFT,驱动TFT3303为p沟道型TFT,像素电极3306a为阳极结构的像素为例来进行表示。

使用图34和图35说明图33结构的像素的驱动方法。另外,图34中,由开关来表示选择TFT3301、保持TFT3302和发光TFT3304,使其导通状态和非导通状态一目了然。另外,(TA1)~(TA4)的各个像素的状态对应于图35的定时图中期间TA1~TA4的状态。

图35中,G_1、G_2、G_3分别表示第一栅极信号线3308、第二栅极信号线3309、第三栅极信号线3310的电位。另外,|Vgs|为驱动TFT3303的栅极电压(栅和源极间电压)的绝对值。IOLED为在OLED3306中流过的电流。Ivideo为由视频信号输入电流源3312确定的电流值。

在期间TA1中,若通过输入到第一栅极信号线3308中的信号,选择TFT3301变为导通状态,另外,通过输入到第二栅极信号线3309中的信号,保持TFT3302变为导通状态,则电源线3311经驱动TFT3303和选择TFT3301与源极信号线3307相连。由于在源极信号线3307中流过由视频信号输入电流源3312确定的电流量Ivideo,所以若经过充分长时间而变为恒定状态,则驱动TFT3303的漏极电流变为Ivideo,并将对应于漏极电流Ivideo的栅极电压保持在保持电容3005中。这时,发光TFT3304为非导通状态。在将电压保持在保持电容3005中,并将驱动TFT3303的漏极电流确定为Ivideo后,在期间TA2中,第二栅极信号线3309的信号改变,保持TFT3302变为非导通状态。

接着,在期间TA3中,第一栅极信号线3308的信号变化,选择TFT3301变为非导通状态。另外,在期间TA4中,若通过输入到第三栅极信号线3310中的信号,发光TFT3304变为导通状态,则信号电流Ivideo从电源线3311经驱动TFT3303的源和漏极间而输入到OLED3306中。这样,OLED3306以根据信号电流Ivideo的亮度发光。

将期间TA1~TA4的一系列动作称为信号电流Ivideo的写入动作。这时,通过模拟改变信号电流Ivideo,改变OLED3306的亮度,而表现灰度等级。

另外,在图35的定时图中,表示在期间TA1中驱动用TFT3303的栅极电压的绝对值|Vgs|随时间经过一起增加,并保持对应于漏极电流Ivideo的栅极电压的动作。其相当于从没有在保持电容3305中保持电荷的状态开始进行写入动作的情况和在前一写入动作中所保持的驱动TFT3303的栅极电压的绝对值|Vgs|比下一写入动作中,流过由视频信号输入电流源3312确定的规定漏极电流时驱动TFT3303的栅极电压的绝对值|Vgs|小的情况。

但是并不限于此,在前一写入动作中所保持的驱动TFT3303的栅极电压的绝对值|Vgs|比下一写入动作中,流过由视频信号输入电流源3312确定的规定漏极电流时驱动TFT3303的栅极电压的绝对值|Vgs|大的情况下,在期间TA1中驱动用TFT3303的栅极电压的绝对值|Vgs|随时间经过减小,而为保持对应于漏极电流Ivideo的栅极电压的动作。

这样,在电流写入型模拟方式的显示装置中,驱动TFT3303在饱和区域中动作。由从源极信号线3307输入的信号电流确定驱动TFT3303的漏极电流。即,驱动TFT3303即使在阈值电压和迁移率等有偏差时,也自动改变栅极电压,像持续流过一定的漏极电流那样。

下面,作为电流写入型模拟方式的像素的其他例子,在图29中表示在特开2001-147659公报中所记载的像素结构,并详细说明其驱动方法。在图29中,由OLED2906、选择TFT2901、驱动TFT2903、电流(current)TFT2904、电容元件(保持电容)2905、保持TFT2902、源极信号线2907、第一栅极信号线2908、第二栅极信号线2909、电源线2911构成像素。

将选择TF2901的栅极与第一栅极信号线2908相连。将选择TFT2901的源极端子与漏极端子中的一个连接到源极信号线2907,另一个连接到电流TFT2904的源极端子或漏极端子和保持TFT2902的源极端子或漏极端子。通过电流TFT2904的源极端子和漏极端子将没有与选择TFT2901相连一侧连接到电源线2911。通过保持TFT2902的源极端子和漏极端子将没有与选择TFT2901相连的一侧连接到保持电容2905的一个电极和驱动TFT2903的栅极上。将保持电容2905的另一侧与电源线2911相连。将保持TFT2902的栅极与第二栅极信号线2909相连。将驱动TFT2903的源极端子和漏极端子的一个连接到电源线2911,另一个与OLED2906的一个电极2906a相连。将OLED2906的另一个电极2906b保持在一定电位上。另外,将OLED2906的连接到驱动TFT2903侧的电极2906a称为像素电极,将另一电极2906b称为对置电极。

在图29所示结构的像素中,构成为由视频信号输入电流源2912控制输入到源极信号线2907的信号电流的电流值。另外,实际上,对应于多个像素列的多个视频信号输入电流源2912相当于源极信号线驱动电路的一部分。

图29中,以通过选择TFT2901、保持TFT2902为n沟道型TFT,驱动TFT2903、电流TFT2904为p沟道型TFT构成的、像素电极2906a为阳极构成的像素为例进行表示。这里,为说明简单,认为驱动TFT2903的电流特性等于电流TFT2904的电流特性。使用图28和图27说明图29构成的像素的驱动方法。另外,由开关来标记图28中选择TFT2901和保持TFT2902,使其导通状态和非导通状态一目了然。另外,(TA1)~(TA3)各个像素的状态对应于图27的定时图中期间TA1~TA3的状态。

图27中,G_1、G_2分别表示第一栅极信号线2908、第二栅极信号线2909的电位。另外,|Vgs|为驱动TFT2903的栅极电压(栅和源极间电压)的绝对值。IOLED为在OLED2906中流过的电流。Ivideo为由视频信号输入电流源2912确定的电流值。

在期间TA1中,若通过输入到第一栅极信号线2908中的信号,选择TFT2901变为导通状态,另外,通过输入到第二栅极信号线2909中的信号,保持TFT2902变为导通状态,则电源线2911经电流TFT2904、保持TFT2902和选择TFT2901与源极信号线2907相连。由于在源极信号线2907中流过由视频信号输入电流源2912确定的电流量Ivideo,所以若为稳定状态,则电流TFT2904的漏极电流变为Ivideo,并将对应于此的栅极电压保持在保持电容2905中。

在将电压保持在保持电容2905中,并将电流TFT2904的漏极电流确定为Ivideo后,在期间TA2中,第二栅极信号线2909的信号改变,保持TFT2902变为非导通状态。这时,在驱动TFT2903中流过Ivideo的漏极电流。这样,信号电流Ivideo从电源线2911经驱动TFT2903输入到OLED2906中。OLED2906以根据信号电流Ivideo的亮度发光。

接着,在期间TA3中,第一栅极信号线2908的信号变化,选择TFT2901变为非导通状态。在选择TFT2901变为非导通状态后,信号电流Ivideo从电源线2911经驱动TFT2903提供给OLED2906,OLED2906继续发光。

将期间TA1~TA3的一系列动作称为信号电流Ivideo的写入动作。这时,通过模拟改变信号电流Ivideo,改变OLED3306的亮度,而表现灰度等级。

如上这样,在电流写入型模拟方式的显示装置中,驱动TFT2903在饱和区域中动作。驱动TFT2903的漏极电流经从源极信号线2907输入的信号电流确定。即,若同一像素内的驱动TFT2903和电流TFT2904的电流特性一致,则驱动TFT2903即使阈值电压和迁移率等有偏差,栅极电压也自动变换,使其持续流过一定的漏极电流。

施加到OLED中的电压和流过的电流量的关系(I-V特性)根据周围的环境温度和OLED的劣化等影响而改变。因此,在线性区域中动作现有的电压写入型的数字方式所代表的驱动TFT的显示装置中,即使在OLED的两电极间施加一定电压,实际上所流过的电流改变也成为问题。

图36表示在现有的电压写入型的使用数字方式驱动方法的显示装置中,因OLED的I-V特性劣化等而改变时的动作点的改变。

图36(A)是仅表示了图30中驱动TFT3004和OLED3006的图。这里,将驱动TFT3004的源极端子连接到电源线3005上。由Vds表示驱动TFT3004的源和漏极间电压。由VOLED表示OLED3006的阴极和阳极间的电压,由IOLED表示电流。电流IOLED相当于驱动TFT3004的漏极电流Id。由Vdd表示电源线3005的电位。另外,将OLED3006的对置电极的电位设为0V。

图36(B)中,曲线3202a表示劣化前的OLED3006的I-V特性,曲线3202b表示劣化后的I-V特性。由曲线3202a和曲线3201的交点3203a确定劣化前的驱动TFT3004和OLED3006的动作条件。由曲线3202b和曲线3201的交点3203b确定劣化后的驱动TFT3004和OLED3006的动作条件。

在选择发光状态的像素中,驱动TFT3004输入栅极电位,使其为导通状态。这时,OLED3006的两电极间的电压为VA1。若OLED3006劣化,其I-V特性改变,则即使输入同一栅极电压,动作点也改变,即使OLFD3006的两电极间的电压与VA1大致相同,所流过的电流也从IOLED1变为IOLED2。这样,由各像素的OLED3006劣化程度改变,OLED3006的发光亮度。

另一方面,在具有图33和图29所示像素结构,使用现有的电流写入型模拟方式的驱动方法的显示装置中,通过在OLED中流过一定电流而表现灰度等级。这时,使用图37说明这时的OLED的I-V特性因劣化等变化时的影响。另外,与图33相同的部分使用同一附图标记表示,而省略说明。另外,在图33中,发光TFT3304可仅认为为开关,而不管其源和漏极间电压。

图37(A)是仅表示图33的驱动TFT3303和OLED3306的图。这里,驱动TFT3303的源极端子被连接到电源线3305。由Vds表示驱动TFT3303的源和漏极间电压。由VOLED表示OLED3306的阴极和阳极间的电压。由IOLED表示在OLED3306中流过的电流。电流IOLED等于驱动TFT3303的漏极电流Id。由Vdd表示电源线3305的电位。将OLED3306的对置电极的电位设为OV。

图37(B)中,3701是表示驱动TFT3303的源和漏极间电压和漏极电流的关系的曲线。3702a是表示劣化前的OLED3306的I-V特性的曲线,3702b是表示劣化后的OLED3306的I-V特性的曲线。由曲线3702a和曲线3701的交点3203a确定劣化前的驱动TFT3303和OLED3306的动作条件。由曲线3702b和曲线3701的交点3203b确定劣化后的驱动TFT3303和OLED3306的动作条件。

在电流写入型模拟方式的像素中,驱动TFT3303在饱和区域动作。在OLED3306的劣化前后,虽然OLED3306的两电极间的电压从VB1变为VB2,但是在OLED3306中流过的电流保持在大致一定的IOLED1。这里所示的对应于OLED的I-V特性的变化的驱动TFT和OLED的动作条件的变化与图29所示的像素结构的驱动TFT2903和OLED2906相同。

但是,在电流写入型模拟方式的驱动方法中,需要每次在各像素中进行显示时,重新将根据信号电流的电荷保持在各像素的电容部(保持电容)。这时,在信号电流越小的情况下布线的交叉电容等成为问题,在将信号写入到像素时,由于在保持电容中保持规定电荷用的时间需要变长,所以信号电流的快速写入变得困难。

另外,在信号电流小的情况下,因进行信号电流的写入的像素之外的,连接到同一源极信号线的多个像素造成的漏电流等的噪声影响变大,不能在正确的亮度下使像素发光的危险性变高。

另外,在图29所示的像素所代表的具有电流镜的像素结构中,在电流镜电路中连接栅极的一组TFT的电流特性必须一致。但是,实际上,成对的TFT的电流特性完全一致很困难,容易产生偏差。

这里,在图29中,将驱动TFT2903和电流TFT2904的阈值分别设为Vtha、Vthb。在这些阈值有偏差,Vtha的绝对值|Vtha|比Vthb的绝对值|Vthb|小时,考察进行黑色显示的情况。电流TFT2903中流过的漏极电流相当于由视频信号输入电流源2912确定的电流值video,设为零。但是,即使在电流TFT2903中没有流过漏极电流,还有可能在保持电容2905中保持比|Vthb|稍小的电压。这里,由于|Vthb|>|Vtha|,所示驱动TFT2903的漏极电流有可能不为0。这样,在进行黑色显示的情况下,在驱动TFT2903中流过漏极电流,OLED2906发光了。因此,存在对比度降低的问题。

进一步,在现有的电流写入型模拟方式的显示装置中,虽然在每个像素列中设置将信号电流输入到各个像素的视频信号输入电流源,但是需要这些电流源的所有电流特性一致,且模拟改变电流值,来进行正确控制。因此,在使用多晶半导体薄膜的晶体管中,制作电流特性一致的视频信号输入电流源是困难的。由此,由IC芯片制作视频信号输入电流源。另一方面,从成本的角度方面,通常形成像素的基板是在玻璃等的绝缘基板(具有绝缘表面的基板)上制作的。因此,IC芯片需要粘附在玻璃等的绝缘基板上。因此,存在在粘附时所需要的面积大,而不能使像素区域周围的框缘面积小的问题。

发明内容

本发明鉴于上述问题而作出,其目的是提供一种可以使发光元件以一定亮度发光,而与由劣化等造成的电流特性的变化无关,且写到各个像素的信号写入速度迅速、可以表现正确的灰度等级,及低成本,可以小型化的显示装置及其驱动方法。

根据本发明的显示装置,包含像素,该像素构成为具有将第一电流变换为电压的单元,保持变换后的所述电压的单元,将所保持的所述电压变换为第二电流的单元和通过数字图像信号,在发光元件中流过所述第二电流的单元。

将所述所保持的所述电压变换为第二电流的单元是变换为与所述第一电流的电流值相等的第二电流,或电流值与所述第一电流成正比的第二电流的单元。

根据本发明的显示装置,具有通过与所述数字图像信号不同的信号而使在所述发光元件中不流过所述第二电流的单元。

另外,本发明的显示装置包含具有流过一定电流的电流源电路,通过数字图像信号进行接通断开切换的开关部的像素,并控制发光元件的发光,串联连接所述开关部、所述电流源电路和发光元件。

另外,本发明的显示装置,含有像素,该像素具有电流源电路,具有第一端子和第二端子,并将所述第一端子和所述第二端子间流过的电流确定为一定;开关部,具有第三端子和第四端子,并通过数字图像信号切换所述第三端子和所述第四端子间的导通和非导通状态;电源线;电源基准线,在所述电源线和所述电源基准线之间连接所述电流源电路、所述开关部和所述发光元件,以便在选择了所述第三端子和所述第四端子间的导通状态时,在所述第一端子和所述第二端子间流过的电流在发光元件的阳极和阴极间流过。

另外,根据本发明的显示装置,包含像素,构成为具有将第一电流设为第一晶体管的漏极电流的单元,保持所述第一晶体管的栅极电压的单元,将所述栅极电压设为与所述第一晶体管极性相等的第二晶体管的栅极电压的单元,通过数字图像信号,在发光元件中流过所述第二晶体管的漏极电流的单元。

在所述显示装置中,所述第一晶体管的栅极长宽比与所述第二晶体管的栅极长宽比不同,同时具有电连接所述第一晶体管的栅极和漏极端子的单元。

另外,所述的显示装置,具有通过与所述数字图像信号不同的信号而使在所述发光元件中不流过所述第二晶体管的漏极电流的单元。

根据本发明的显示装置,包含像素,构成为具有将第一电流输入到晶体管中而作为所述晶体管的漏极电流的单元,保持所述晶体管的栅极电压的单元,通过数字图像信号将电压施加到所述晶体管的源和漏极端子间,并在发光元件中流过由所保持的所述栅极电压所决定的所述晶体管的漏极电流的单元。

所述显示装置在进一步具有电连接所述晶体管的栅极和漏极端子的单元的同时,具有通过与所述数字图像信号不同的信号而使在所述发光元件中不流过所述晶体管的漏极电流的单元。

在所述显示装置中,所述第一电流不根据所述数字图像信号变化。

在所述显示装置中,所述像素具有选择向所述像素的所述数字图像信号的输入的单元和保持所述数字图像信号的单元。

另外,所述显示装置具有多个所述像素,在多个所述像素的至少一部分中所述第一电流的电流值相同。

进一步,本发明的显示装置具有将一定电流输入到所述像素的驱动电路。

根据本发明的显示装置的驱动方法,在像素中进行将所输入的第一电流变换为电压,保持所变换的所述电压的第一步骤和通过所输入的数字图像信号,将所保持的所述电压变换为第二电流,并在发光元件中流过所述第二电流的第二步骤。

在所述驱动方法,所述第二步骤包含选择向所述像素的所述数字图像信号的输入,并保持所输入的所述数字图像信号的动作,且独立进行所述第一步骤和所述第二步骤。

在所述驱动方法中,通过改变流过所述第二电流期间在一帧期间的所述发光元件中的比例,来表现灰度等级。

另外,所述驱动方法包含,将一帧期间分割为多个子帧期间,并在各个所述多个子帧期间,进行所述第二步骤,来表现灰度等级,在所述多个子帧期间的至少一个中设置非显示期间,使得通过与所述数字图像信号不同的信号不在所述发光元件中流过所述第二电流,并在所述非显示期间,进行所述第一步骤。

接着,使用图1说明上述公开的根据本发明的显示装置及其驱动装置。

图1是表示本发明的显示装置的像素结构的模式图。本发明的显示装置的各个像素具有电流源电路和开关部和发光元件。在电源基准线和电源线间串联连接发光元件、电流源电路和开关部。另外,所谓电流源电路是指流过所规定的一定电流的电路。另外,若为通过电流或电压等控制状态的元件,发光元件可以任意。作为例子,举出有EL元件(尤其是将使用有机材料的元件称为OLED等)和FE(Field Emission)元件等。除此之外,若为通过电流或电压等控制状态的元件,也可以适用于本发明。

OLED构成为具有阳极和阴极、在其间夹着的有机化合物层等。阳极和阴极分别对应于第一电极和第二电极,并通过将电压施加到这些电极间,OLED发光。有机化合物层通常为层积结构。代表性的,可举出为“空穴输送层/发光层/电子输送层”的层积结构。除此之外,也可以是在阳极上以空穴注入层/空穴输送层/发光层/电子输送层,或空穴注入层/空穴输送层/发光层/电子输送层/电子注入层的顺序层积的结构。对于发光层也可掺杂荧光性色素等。将在阳极和阴极间设置的所有层统称为有机化合物层。由此,上述的空穴注入层、空穴输送层、发光层、电子输送层、电子注入层等所有包含在有机化合物层中。对于上述结构的有机化合物层,若从一对电极(阳极和阴极)施加规定的电压,则在发光层中引起载流子的重新结合而发光。另外,OLED使用一重项激励子的发光(荧光)和使用三重项的发光(磷光)的其中一种。

图1代表性地表示在电源基准线和电源线间以发光元件、开关、电流源电路的顺序串联连接的结构。本发明并不限于此,例如也可以是在以发光元件、电流源电路、开关部的顺序在电源基准线和电源线间串联连接的结构。即,发光元件、电流源电路、开关部也可以以任何顺序在电源基准线和电源线间串联连接。另外,也可设置多个开关部。例如,也可以在电源基准线和电源线间串联连接发光元件、第一开关部和第二开关部、电流源电路的结构。另外,开关部也可以是与电流源电路共有其一部分的结构。即,也可以为使用构成电流源电路的元件的一部分来作为开关部的结构。

通过使用数字图像信号,切换开关部的接通断开(导通和非导通)。另外,由从像素外部输入的控制信号决定在电流源电路中流过的一定电流的大小。在开关部为开状态的情况下,在发光元件上流过由电流源电路确定的一定电流而发光。开关部为断开状态时,发光元件中不流过电流,不发光。这样,通过图像信号控制开关部的接通断开而表现灰度等级。

在设置了多个开关部的情况下,切换这些开关部的各个的接通断开的信号可以是图像信号、其他任何信号或图像信号和其他任意信号双方。但是,多个开关部中至少一个开关部需要通过图像信号切换接通断开。例如,在电源基准线和电源线间构成为串联连接发光元件、第一开关部、第二开关部和电流源电路的情况下,可以构成为第一开关部通过图像信号切换接通断开,第二开关部通过与图像信号不同的信号切换接通断开。另外,也可以构成为第一开关部、第二开关部同时由图像信号切换接通断开。

在本发明的显示装置中,除了驱动开关部的图像信号之外,输入决定在电流源电路中流过的一定电流用的控制信号。作为控制信号,可以是电压信号和电流信号的其中之一。另外,也可任意决定向电流源电路输入控制信号的定时。也可以同步进行将控制信号输入到电流源电路与将图像信号输入到开关部,也可以不同步进行。

在本发明的显示装置中,在进行图像显示时,由于将在发光元件中流过的电流保持为一定,可以以一定亮度使发光元件发光,而与因劣化等造成的电流特性的变化无关。

在本发明的显示装置中,由与图像信号不同的信号控制在配置在各像素的电流源电路中流过的电流大小,通常为一定。另外,其特征在于使用数字图像信号驱动开关部,选择在发光元件中流过一定电流或不流过一定电流,切换发光和非发光状态,而以数字方式表现灰度等级。

在本发明的显示装置的像素结构中,在没有通过图像信号选择发光状态的像素中,由于通过开关部完全隔断输入到发光元件中的电流,而可表现准确的灰度等级。即,为显示黑色,可以避免少量发光。因此,可以抑制对比度降低。另外,由于通过以数字图像信号选择开关部的接通断开状态,选择各像素的发光状态或非发光状态,所以可以加速将图像信号写入到像素中。

在现有的电流写入型模拟方式的像素结构中,需要根据亮度减小输入到像素中的电流,而存在噪声影响变大的问题。另一方面,在本发明的显示装置的像素结构中,若将在电流源电路中流过的一定电流的电流值设定为增加某一程度,则可以降低噪声的影响。

另外,在现有的电流写入型模拟方式的像素的情况下,图像信号为电流。因此,为了重写图像信息,必定需要以根据该亮度的电流值重写像素所保持的图像信息。这时,由于一帧期间为1/60秒,所以在该时间内需要在每一帧中重写所有像素的图像信息。因此,若决定显示装置的标准(例如,像素数等),则必须在每一像素所决定的时间内重写图像信息。由此,尤其是信号电流的值小时,因布线的负载(交叉电容和布线电阻等)的影响在所决定的时间内准确重写图像信息变得困难。

但是,在本发明中,输入与图像信号不同的控制信号,并决定在像素的电流源电路中流过的电流值。并且,输入控制信号的定时和所输入的期间、所输入的周期为任意。由此,可以避免进入现有情况下的状态。

进一步,在现有的电流写入型模拟方式的显示装置中,需要将对应于图像信号的模拟信号电流输入到配置在各像素中的电流源电路中用的驱动电路。由于该驱动电路最好对各个像素准确输出模拟信号电流,所以需要由IC芯片制作。因此,具有成本提高,小型化难的问题。另一方面,在本发明的显示装置中,不需要使在配置在各个像素中的电流源电路中流过的电流的值配合图像信号变化用的驱动电路。即,由于构成为不需要由IC制作的外置的驱动电路,所以可以实现低成本和小型化。

这样,可以提供以一定亮度使发光元件发光,而与因劣化等引起的电流特性的变化无关,并且,提高将信号写入到各像素的速度,可表现准确的灰度等级、低成本且可小型化的显示装置及其驱动方法。

附图说明

图1是表示本发明的显示装置的像素驱动方法的模式图;

图2是表示使用了本发明的显示装置的显示系统的图;

图3是表示本发明的显示装置的像素结构的框图;

图4是本发明的显示装置的电流源电路的电路图;

图5是本发明的显示装置的像素部的电流图;

图6是表示本发明的显示装置的像素设定动作的定时图;

图7是表示本发明的显示装置的像素显示动作的定时图;

图8是表示本发明的显示装置的基准电流输入电路的结构框图;

图9是表示本发明的显示装置的基准电流输入电路的结构框图;

图10是显示表示本发明的显示装置的基准电流输入电路的动作的定时图;

图11是表示本发明的显示装置的基准电流输入电路的动作方法的图;

图12是本发明的显示装置的电流源电路的电路图;

图13是本发明的显示装置的开关部的电路图;

图14是本发明的显示装置的像素部的电路图;

图15是表示本发明的显示装置的像素设定动作的定时图;

图16是表示本发明的显示装置的像素显示动作及其定时图;

图17是本发明的显示装置的电流源电路的电路图;

图18是本发明的显示装置的像素部的电路图;

图19是表示本发明的显示装置的像素设定动作的定时图;

图20是表示本发明的显示装置的参考电流源电路的切换电路的结构图;

图21是本发明的显示装置的电流源电路的电路图;

图22是本发明的显示装置的像素部的电路图;

图23是本发明的显示装置的电流源电路的电路图;

图24是本发明的显示装置的电流源电路的电路图;

图25是本发明的显示装置的电流源电路的电路图;

图26是本发明的显示装置的像素部的电路图;

图27是表示现有的显示装置的驱动方法的定时图;

图28是表示现有的显示装置的驱动方法的图;

图29是现有的显示装置的像素的电路图;

图30是现有的显示装置的像素的电路图;

图31是表示现有的显示装置的驱动晶体管的动作区域的图;

图32是表示现有的显示装置的驱动晶体管的动作点的图;

图33是现有的显示装置的像素的电路图;

图34是表示现有的显示装置的驱动方法的图;

图35是表示现有的显示装置的驱动方法的定时图;

图36是表示因现有的显示装置的发光元件劣化带来的驱动晶体管的动作点变化的图;

图37是表示因现有的显示装置的发光元件劣化带来的驱动晶体管的动作点变化的图;

图38是表示本发明的显示装置的电流源电路的结构的图;

图39是表示本发明的显示装置的像素部结构的图;

图40是表示本发明的显示装置的像素显示动作及其定时图;

图41是表示本发明的显示装置的电流源结构的图;

图42是表示本发明的显示装置的像素部结构的图;

图43是本发明的显示装置的像素开关部的电路图;

图44是表示本发明的显示装置的电流源电路的结构的图;

图45是表示本发明的显示装置的像素部结构的图;

图46是表示应用本发明的显示装置的电子设备的图;

图47是表示本发明的显示装置的电流源电路结构的图;

图48是表示本发明的显示装置的像素部结构的图;

图49是表示本发明的显示装置的驱动方法的定时图;

图50是表示本发明的显示装置的像素部结构的图;

图51是表示本发明的显示装置的像素部结构的图;

图52是表示本发明的显示装置的像素部结构的图;

图53是表示本发明的显示装置的像素部结构的图;

图54是表示本发明的显示装置的信号线驱动电路的结构框图;

图55是表示本发明的显示装置的信号线驱动电路的结构图;

图56是表示本发明的显示装置的扫描线驱动电路的结构图;

图57是表示本发明的显示装置的电流源电路的结构图;

图58是表示本发明的显示装置的电流源电路的结果图;

图59是显示表示本发明的显示装置的像素的设定动作的定时图;

图60是本发明的显示装置的扫描线驱动电路的结构图;

图61是表示本发明的显示装置的像素状态的模式图;

图62是表示本发明的显示装置的像素状态的模式图;

图63是表示本发明的显示装置的像素状态的模式图;

图64是表示本发明的显示装置的像素状态的模式图;

图65是表示本发明的显示装置的像素状态的模式图;

图66是表示本发明的显示装置的像素状态的模式图;

图67是本发明的显示装置的像素的电流源电路的电路图;

图68是本发明的显示装置的像素的电流源电路的电路图;

图69是本发明的显示装置的像素的电流源电路的电路图;

图70是本发明的显示装置的像素的电流源电路的电路图;

图71是本发明的显示装置的像素的电流源电路的电路图;

图72是本发明的显示装置的像素的电流源电路的电路图;

图73是表示本发明的显示装置的像素结构的电路图;

图74是表示本发明的显示装置的像素结构的电路图;

图75是表示本发明的显示装置的像素结构的电路图;

图76是表示本发明的显示装置的像素结构的电路图;

图77是表示本发明的显示装置的像素结构的电路图;

图78是表示本发明的显示装置的像素结构的俯视图(A)和电路图(B);

图79是表示本发明的显示装置的像素结构的俯视图(A)和电路图(B)。

具体实施例

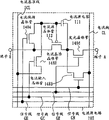

图3(A)表示本发明的显示装置的像素结构的模式图。在图3(A)中,各个像素100由扫描线G、图像信号输入线S、电源线W、开关部101、电流源电路102和发光元件106构成。

在各个像素100中,开关部101具有端子C和端子D。将发光元件106的像素电极106a与开关部的端子D相连。开关部的端子C与电流源电路102的端子B相连。将电流源电路102的端子A与电源线W相连。电流源电路102由圆圈中配置了箭头的符号来模式表示。电流源电路102为该符号的箭头方向,即为从端子A向端子B的方向流过正的一定电流的电路。将端子A或端子B的一个称为电流源电路102的输入端子,将另一个称为电流源电路102的输出端子。

在从图像信号输入线S输入选择发光状态的信号的像素100中,开关部101的端子C和端子D之间为导通状态。由此,经开关部101的端子C和端子D间和电流源电路102的端子A和端子B间,发光元件106的像素电极106a与电源线W相连。

开关部101具有根据从扫描线G输入的信号切换将图像信号输入线S上的图像信号对像素的输入的第一开关和根据输入到像素中的图像信号进行接通断开切换的第二开关。通过切换第二开关的接通断开,而切换开关部的端子C和端子D间的导通和非导通状态。将端子C或端子D的一个称为开关部101的输入端子,将另一个称为开关部101的输出端子。

发光元件106表示从像素电极106a向对置电极106b或其反方向流过电流,并根据该电流改变亮度的元件。

在图3(A)中,由于电流源电路102的端子A连接到电源线W,端子B经开关部101的端子C和端子D间连接到发光元件106的像素电极106a,所以发光元件106的像素电极106a变为阳极,对置电极106b变为阴极。这时,设定为提供给像素元件106a的对置电极106b的电位Vcom比电源线W的电位低。由电源基准线(图中未示)提供给电位Vcom。

另一方面,也可构造为将电流源电路102的端子A连接到开关部101的端子C,将端子B连接到电源线W。这时,发光元件106的像素电极106a变为阴极,对置电极106b变为阳极。而设定为提供给像素元件106a的对置电极106b的电位Vcom比电源线W的电位高。

另外,由于电流源电路102、开关部101和发光元件106的连接顺序可以任意,例如可以将电流源电路102配置在开关部101和发光元件106间。即,也可将电流源电路102的端子B与发光元件106的像素电极106a相连,电流源电路102的端子A与开关部101的端子D相连,开关部101的端子C连接到电源线W。进一步,也可为反转电流源电路102的端子A和端子B的结构。即,也可将电流源电路102的端子A与发光元件106的像素电极106a相连,电流源电路102的端子B与开关部101的端子D相连,开关部101的端子C连接到电源线W。该情况下,发光元件106的像素电极106a变为阴极,对置电极106b变为阳极。这时,设定为提供给像素元件106a的对置电极106b的电位Vcom比电源线W的电位高。

在开关部101中,在端子C和端子D间为导通状态的像素100中,将由电流源电路102确定的一定电流输入到发光元件106,发光元件106发光。

图3(B)和图3(C)表示电流源电路102的基本结构例。举例为在各像素的电流源电路中流过的一定电流是由电流信号确定的电流源电路的例子。将这种结构的电流源电路称为电流控制型电流源电路。图3(B)和图(C)中的端子A和端子B对应于图3(A)中的端子A和端子B。

在图3(B)和图3(C)中,电流源电路102具有晶体管(电流源晶体管)112和电容元件(电流源电容)111。在饱和区域中动作的电流源晶体管112的漏极电流为对应于从像素外部输入的一定电流(下面,记为基准电流)的一定电流(下面,记为像素基准电流)。即,从像素外部输入一定电流(基准电流)。若由电流源电容111保持这时的栅极电压Vgs(下面,记为像素对应基准电压),则在电流源晶体管112在饱和区域动作的情况下,将对应于基准电流的一定电流(像素基准电流)作为漏极电流流到电流源晶体管112和发光元件106中。这样,从外部电流源不再输入基准电流后,若电流源晶体管112还在源和漏极间施加电压,则根据保持在电流源电容111中的像素对应基准电压而流过像素基准电流。另外,也可通过使用其他晶体管的栅极电容等而省略电流源电容111。

在配置在各个像素中的电流源电容111中,取得并保持将电流源晶体管112流过像素基准电流所需的栅极电压的动作称为像素设定动作。另外,作为本发明的晶体管,可以是薄膜晶体管(TFT)和单结晶晶体管等的晶体管的其中一种。

另外,也可以是使用有机物的晶体管。例如,作为单结晶晶体管也可是使用SOI技术而形成的晶体管。作为薄膜晶体管,可将多晶半导体用作活性层,也可以是使用非晶质半导体作为活性层。例如,可以是使用聚合硅的TFT或使用非晶硅的TFT。

在电流源电路102中,在电流源晶体管112中流过漏极电流时,将电流源电容111的一个电极与电流源晶体管112的栅极相连,并对另一个(图中由端子A表示)提供一定电位。通过保持在电流源电容111中的电荷,保存在电流源晶体管112的栅极的电位(栅极电位)。这里,虽然端子A`的电位与电流源晶体管112的源极端子的电位也可相同也可不同,但是在电流源晶体管中流过像素基准电流时,各个端子间的电位差也总是相同。这样,在电流源晶体管112中保持流过像素基准电流时的栅极电压Vgs(像素对应基准电压)。在饱和区域动作的晶体管中,根据栅极电压Vgs漏极电流也变化。因此,最好将端子A’连接到源极端子,使得即使源极端子的电位变化,栅极电压Vgs也一定。另外,在图3(B)和图3(C)中,电流源晶体管112的极性不同。在图3(B)中,电流源晶体管112为p沟道型,在图3(C)中为n沟道型。

在如图3(A)所示相连的情况下,在电流源晶体管112为p沟道型的情况下,电流源晶体管112从源极端子向漏极端子流过电流。另外,在电流源晶体管112为n沟道型的情况下,从电流源晶体管112的漏极端子向源极端子流过电流。因此,在电流源晶体管112为p沟道型的情况下,将电流源晶体管112的源极端子连接到端子A,将漏极端子连接到端子B。另一方面,在电流源晶体管112为n沟道型的情况下,将电流源晶体管112的漏极端子连接到端子A’,将源极端子连接到端子B。

作为通过从像素外部输入的电流信号(基准电流)控制像素基准电流的手段,大致分为两种方法。

一种是命名为电流镜方式的方式。电流镜电路具有电连接栅极的一对晶体管,具有电连接一个晶体管的栅极和漏极端子的结构。在电流镜方式中,是在构成电流镜电路的一对晶体管中,将一个晶体管作为电流源晶体管112,将另一个晶体管作为电流晶体管。电连接电流晶体管的漏极端子和栅极,并将基准电流输入到其源和漏极间的方法。

另一种是命名为同一晶体管方式的方式。在同一晶体管方式是电连接漏极端子和栅极的电流源晶体管112的源和漏极间直接输入基准电流的方法。另外,作为同一晶体管方式的变形,称为多栅极方式。

将使用电流镜方式的电流源电路称为电流镜方式的电流源电路,将使用同一晶体管方式的电流源电路称为同一晶体管方式的电流源电路,将使用多栅极方式的电流源电路称为多栅极方式的电流源电路。电流源电路102一旦输入基准电流,就在电流源电容111中保持像素对应基准电压,在进行了像素的设定动作后,只要不放电在电流源电容111中保持的电荷,就没有必要再次输入基准电流的动作。

保持在电流源电容111中的电荷实际上因泄漏电流的影响和各种噪声而随时间经过改变。这里,需要定期反复进行像素的设定动作。但是,一旦在进行了像素设定动作之后,在定期进行像素的设定动作中,也可重新保持因泄漏电流而在电流源电容111中保持的电容改变了的部分的电荷。因此,与初始的像素设定动作相比,其后定期进行像素的设定动作所需的时间变短了。

(实施形式1)

表示本发明的显示装置的像素结构的一例。图4表示配置在各个像素中的电流源电路的结构例。另外,在图4中,表示为与图3相同的部分使用同一附图标记。图4表示电流镜方式的电流源电路的例子。电流源电路102由电流源电容111、电流源晶体管112、电流晶体管1405、电流输入晶体管1403、电流保持晶体管1404、电流线CL、信号线GN和信号线GH构成。由于电流源晶体管112和电流晶体管1405一对构成了电流镜电路,所以极性必须相等。另外,最好同一像素内的这两个晶体管的电流特性相同。这里,在本实施形式1中,为了简单起见,设电流源晶体管112和电流晶体管1405的电流特性相同。

在图4中表示电流源晶体管112和电流晶体管1405为p沟道型的例子。另外,即使在电流源晶体管112和电流晶体管1405为n沟道型的情况下,根据图3(C)所示的结构,也可容易应用。图23表示该情况的例子。在图23中表示为与图4相同的部分使用相同的附图标记。在图23中,为防止在像素设定动作时在电流源晶体管112中流过电流,而设置追加晶体管1801和1803。即,在像素的设定动作时,追加晶体管1801和1803为非导通状态。另一方面,在进行像素显示时为导通状态。另外,为防止在进行像素显示时在电流晶体管1405中流过电流,而设置追加晶体管1802。即,在像素的设定动作时,追加晶体管1802为导通状态。另一方面,在进行像素显示时,为非导通状态。

下面,以图4为例进行说明。虽然电流输入晶体管1403、电流保持晶体管1404为n沟道型,但由于仅作为开关动作,故也可为p沟道型。

将电流源晶体管112的栅极和电流晶体管1405的栅极及电流源电容111的一个电极相连。另外,将电流源电容111的另一电极与电流源晶体管112的源极端子及电流晶体管1405的源极端子相连,并连接到电流源电路102的端子A上。电流晶体管1405的栅极和漏极端子经电流保持晶体管1404的源和漏端子间相连。将电流保持晶体管1404的栅极连接到信号线GH上。将电流晶体管1405的漏极端子和电流线CL经电流输入晶体管1403的源和漏端子间相连。将电流输入晶体管1403的栅极与信号线GN相连。另外,将电流源晶体管112的漏极端子连接到端子B上。

另外,在上述结构中,也可将电流输入晶体管1403配置在电流晶体管1405和端子A之间。即,也可以是将电流晶体管1405的源极端子经电流输入晶体管1403的源和漏极端子间与端子A相连,将电流晶体管1405的漏极端子连接到电流线CL的结构。

另外,在上述结构中,也可将电流晶体管1405和电流源晶体管112的栅极连接到电源线CL,而不经电流输入晶体管1403的源和漏极端子间。即,也可以是电流保持晶体管1404的源极端子和漏极端子的没有与电流晶体管1405和电流源晶体管112的栅极相连侧连接到电流线CL的结构。在该情况下,通过调整电流线CL的电位,也可减小电流保持晶体管1404的源和漏极间电压。结果,在电流保持晶体管1404为非导通状态时,也可减小电流保持晶体管1404的泄漏电流。

但并不限于此,电流保持晶体管1404也可进行连接,使得在导通状态时,电流晶体管1405的栅极电位与电流线CL的电位相等。即,也可在像素设定动作时,变为如图61(a)那样,在发光时变为如图61(b)那样。即,这样,也可连接布线和开关。因此,也可为图67那样。另外,在图67中,表示为与图4相同的部分使用同一附图标记,而省略说明。

接着,图13表示图3(A)的开关部的结构例。另外,在图13中,表示为与图3相同的部分使用同一附图标记。在图13中,开关部101由三个晶体管(选择晶体管301、驱动晶体管302和删除晶体管304)和一个电容元件(保持电容303)构成。也可通过使用晶体管的栅极电容等而省略保持电容303。

在图13中,虽然驱动晶体管302为p沟道型,选择晶体管301和删除晶体管304为n沟道型,但并不限定该结构。由于仅作为开关动作,所以选择晶体管301、驱动晶体管302和删除晶体管304分别可以是n沟道型,也可以是p沟道型。

另外,也可在饱和区域动作驱动晶体管302。通过在饱和区域使驱动晶体管302动作,也可补偿与驱动晶体管302串联连接的电流源电路的电流源晶体管112的饱和区域特性。所谓饱和区域特性,表示对源和漏极间电压漏极电流保持为一定的特性。另外,所谓补偿饱和区域特性,意味着在饱和区域动作的电流源晶体管112中,抑制随源和漏极间电压增加,漏极电流增加。另外,为得到上述效果,驱动晶体管302和电流源晶体管112必须为相同极性。

下面,说明上述的补偿饱和区域特性的效果。例如,着眼于电流源晶体管112的源和漏极间电压增加的情况。串联连接电流源晶体管112和驱动晶体管302。由此,随着电流源晶体管112的源和漏极间电压的变化,驱动晶体管302的源极端子的电位也变化。这样,若驱动晶体管302的源和栅极间电压的绝对值减小,驱动晶体管302的I-V曲线变化。该变化的方向是漏极电流减小的方向。这样,串联连接到驱动晶体管302的电流源晶体管112的漏极电流减小。同样,若电流源晶体管112的源和漏极间电压减小,则电流源晶体管112的漏极电流增加。这样,得到将在电流源晶体管112中流过的电流保持为一定的效果。

下面详细说明图13的开关部的结构。将选择晶体管301的栅极连接到扫描线G。选择晶体管301的源极端子和漏极端子一个连接到图像信号输入线S,另一个连接到驱动晶体管302的栅极。驱动晶体管302的源极端子和漏极端子一个连接到端子D,另一个连接到端子C。保持电容303的一个电极连接到驱动晶体管302的栅极,另一个电极连接到布线Wco。删除晶体管304的源极端子和漏极端子一个与驱动晶体管302的栅极相连,另一个连接到布线Wco。将删除晶体管304的栅极连接到删除用信号线RG。

另外,删除晶体管304的源极端子和漏极端子并不限于上述连接结构。也可以是根据删除晶体管304为导通状态,而放电保持在保持电容303中的电荷那样的各种连接结构。即,也可以是通过使删除晶体管304导通或非导通,而非导通驱动晶体管302的连接结构。

接着,说明图13所示的开关部、删除晶体管304的配置方法不同的结构。图43(A)表示开关部的一例。表示为与图13相同的部分使用同一附图标记而省略说明。在图43(A)中,通过在输入到发光元件的电流路径上串联配置删除晶体管304,使删除晶体管304为非导通状态,而强制地不在发光元件上流过电流。若满足该条件,也可将删除晶体管304配置在任何地方。通过使删除晶体管304为非导通状态,而可使像素一律为非发光的状态。

图43(B)表示开关部101的其他结构。图43(B)为经删除晶体管304的源和漏极端子间向驱动晶体管302的栅极施加规定的电压,而使驱动晶体管302为非导通状态的方法。表示为与图13相同的部分使用同一附图标记而省略说明。在该例中,将删除晶体管304的源极端子和漏极端子的一个连接到驱动晶体管302的栅极,将另一个连接到布线Wr。也可适当决定布线Wr的电位。这样,在布线Wr的电位经删除晶体管304输入到驱动晶体管302的栅极时,使得驱动晶体管302为非导通状态。

另外,在图43(B)所示的结构中,也可代替删除晶体管304而使用二极管。图43(C)表示该结构。改变布线Wr的电位,而改变二极管3040的两个电极中没有与驱动晶体管302的栅极相连侧的电极的电位。由此,可以改变驱动晶体管302的栅极电压,而使驱动晶体管302为非导通状态。另外,二极管3040也可使用二极管连接(电连接栅极与漏极端子)的晶体管。这时,作为晶体管可以为n沟道型也可为p沟道型。另外,也可代替布线Wr而使用扫描线G。图43(D)表示代替图43(B)中布线Wr,而使用扫描线G。需要考虑扫描线G的电位,注意选择晶体管301的极性。

下面说明具有上述结构的电流源电路和开关部的像素。图5表示具有图4所示结构的电流源电路102和具有图13所示结构的开关部101的像素100按x列y行的矩阵状配置的像素区域一部分的电路图。图5中,仅代表性地示出第i(i为自然数)行j(j为自然数)列、第(i+1)行j列、第i行(j+1)列、第(i+1)行(j+1)列四个像素。表示为与图4和图13相同的部分使用同一附图标记而省略说明。

另外,将对应于第i行、第(i+1)行的各个像素行的扫描线标记为Gi、Gi+1,删除用信号线标记为RGi、RGi+1,信号线GN标记为GNi、GNi+1、信号线GH标记为GHi、GHi+1。另外,将对应于第j列、第(j+1)列各个像素列的图像信号输入线S标记为Sj、Sj+1,电源线W标记为Wj、Wj+1,电流线CL标记为CLj、CLj+1,布线Wco标记为Wcoj、Wcoj+1。从像素区域外部将基准电流输入到电流线CLj、CLj+1中。

图5表示发光元件的像素电极为阳极,对置电极为阴极的结构。即,表示将电流源电路的端子A连接到电源线W,将端子B连接到开关部101的端子C的结构。但是,也可容易地将本实施形式1的结构应用于发光元件106的像素电极为阴极,对置电极为阳极结构的显示装置。下面,图26表示在图5所示结构的像素中,发光元件106的像素电极变为阴极,对置电极变为阳极的例子。这样,仅通过改变晶体管的极性而可容易对应。图26中,表示为与图5相同的部分使用同一附图标记,而省略说明。图5中,电流源晶体管112和电流晶体管1405为p沟道型。另一方面,在图26中,电流源晶体管112和电流晶体管1405为n沟道型。这样,流过的电流方向也可为反方向。这时,将图26的端子A与开关部的端子C相连,将端子B与电源线W相连。

另外,在图5和图26中,由于驱动晶体管302仅具有开关功能,所以可以是n沟道型和p沟道型的其中之一。但是,最好驱动晶体管302在其源极端子的电位为固定的状态下动作。因此,在图5所示的发光元件106的像素电极为阳极,对置电极为阴极的结构中,最好驱动晶体管302是p沟道型。另一方面,如图26所示的发光元件106的像素电极为阴极,对置电极为阳极的结构中,最好驱动晶体管302是n沟道型。

另外,在图5中,由于各个像素的布线Wco和电源线W可以保持为同一电位,所以可以共用。另外,也可以共用不同像素间的各个布线Wco、各个电源线W、布线Wco和电源线W。还可共用GNi和GHi。进一步,还可代替布线Wco和布线Wj,而使用其他像素行的扫描线。其可以使用在没有进行图像信号写入的期间,扫描线的电位保持为一定电位的情况。例如,代替电源线,也可使用前一像素行的扫描线Gi-1。但是这时,需要考虑扫描线G的电位,注意选择晶体管301的极性。

虽然图5中没有图示,但是将信号输入到扫描线G的驱动电路(下面,记为扫描线驱动电路)、将信号输入到删除用信号线RG的驱动电路(下面,记为删除用信号线驱动电路)和将信号输入到图像信号输入线S的驱动电路(下面,记为信号线驱动电路)可以自由使用公知结构的电压信号输出型的驱动电路。另外,将信号输入到其他信号线的驱动电路也可自由使用公知结构的电压信号输出型的驱动电路。

404模式表示为决定在电流线CLj、CLj+1中流过的基准电流,在基准电流输出电路的外部设置的电流源电路(下面,记为参考电流源电路)。可以使用来自一个参考电流源电路404的输出电流,来决定在多条电流线CL上流过的基准电流。这样,可以抑制在各电流线上流过的电流偏差,而正确将在所有电流线上流过的电流决定为基准电流。

另外,在本实施形式1中,表示共有决定在所有电流线CL1~CLX中流过的基准电流的参考电流源电路404的例子。使用由参考电流源电路404决定的电流,将基准电流输出到各电流线CL1~CLX用的电路称为基准电流输出电路,并由图5中的405表示。

图8表示基准电流输出电路405的结构。基准电流输出电路405具有移位晶体管等的脉冲输出电路711。对应各电流线CL1~CLX设置输入来自脉冲输出电路711的采样脉冲的采样脉冲线710_1~710_x。代表性地说明对应于某一条电流线CLj的结构。设置输入采样脉冲线710_j的信号的电流输入开关701_j和电流源电路700_j与经反相器703_j输入采样脉冲线710_j的信号的电流输出开关702_j。电流源电路700_j经电流输入开关701_j与参考电流源电路404相连,经电流输出开关702_j与电流线CLj相连。

在图8所示的基准电流输出电路405中,图9表示具体表示电流源电路700_1~700_x的结构例子。在图9中,表示为与图8相同的部分使用同一附图标记。另外,基准电流输出电路405并不限于图8、图9所示的电路。电流源电路700_1~700_x分别具有电流源晶体管720_j、电流源电容721_j和电流保持开关722_j。电流源晶体管720_j经电流源电容721_j连接栅极和源极端子,经电流输入开关722_j连接栅极和漏极端子。将采样脉冲线710_j的信号输入到电流输入开关722_j中。将电流源晶体管720_j的源极端子保持在一定电位,并将漏极端子经电流输入开关701_j与参考电流源电路404相连,经电流输出开关702_j与电流线CLj相连。

另外,也可以是将电流源电容721_j的电极的一个保持在一定电位上,另一个经电流输入开关701_j与参考电流源电路404相连,且经电流输出开关702_j与电流线CLj相连的结构。

另外,在图9中,电流源晶体管720_j也可以是n沟道型和p沟道型的任何一个。但是,最好电流源晶体管720_j在固定源极端子的电位的状态下动作。因此,在从电流源电路700_j向电流线CLj流过电流的情况下,电流源晶体管720_j最好为p沟道型,在从电源线CLj向电流源电路700_j流过电流的情况下,电流源晶体管720_j最好为n沟道。最好是在任何一种极性下,都在栅和源极间连接电流源电容721_j。

使用图10和图11说明图9所示结构的基准电流输出电路405的驱动方法。图10是表示基准电流输出电路405的驱动方法的定时图。另外,图11是模式表示基准电流输出电路405的驱动方法的图。另外,在图10中模式表示各个期间TD1、TD2期间的基准电流输出电路405的各个开关(电流输入开关、电流输出开关、电流保持开关)的开和关状态的图为图11(TD1)、图11(TD2)。

在期间TD1中,若从脉冲输出电路711向采样脉冲线710_1输出脉冲,则电流输入开关701_1和电流保持开关722_1为开状态。另一方面,电流输出开关702_1经反相器703_1输入输出到采样脉冲线710_1的信号,而为关状态。这时,由参考电流源电路404确定的基准电流经电流输入开关701_1和电流保持开关722_1而输入到电流源电路700_1的电流源电容721_1中。另外,这时,不将脉冲输出到其他采样脉冲线710_2~710_x中。因此,电流输入开关701_2~701_x和电流保持开关722_2~722_x为关状态。另一方面,电流输出开关702_2~702_x为开状态。随时间经过,将电荷保持在电流源电路700_1的电流源电容721_1中,而在电流源晶体管720_1中流过基准电流。图10表示在电流源电容721_1的两电极间保持的电荷量即电压的变化。

之后,开始期间TD2。在期间TD2中改变脉冲输出电路711的输出,且不将脉冲输出到采样脉冲线710_1中。由此,电流保持开关722_1和电流输入开关701_1为关状态,电流输出开关702_1为开状态。这样,为在电流线CL1中流过电流源晶体管720_1的漏极电流的状态。这里,由在电流源电容721_1中保持的电荷决定电流源晶体管720_1的漏极电流。由此,将在电流线CL1中流过的电流确定为基准电流。在图10中,CL1~CLX表示在电流线CL1~CLX中流过的电流。同时,将脉冲输出到采样脉冲线710_2。这样,开始将电流源电路700_2中流过的电流确定为基准电流的动作。对于对应于所有采样脉冲线710_1~710_x的电流源电路700_1~700_x进行相同的动作,而终止期间TD1~TDx。这样,将所有电流线CL1~CLX中流过的电流确定为由参考电流源电路404决定的基准电流。

这里,将电流输入到基准电流输出电路405,将在各电流线CL1~CLx中流过的电流决定为基准电流的动作称为基准电流输出电路405的设定动作。

在图9所示结构的基准电流输出电路405的结构中,一旦通过参考电流源电路404,将在各电流源电路700_1~700_x中流过的电流决定为基准电流后,只要不放电在电流源电容721_1~721_x中保持的电荷,则在各电流源电路700_1~700_x中流过的电流保持为基准电流。另外,如图9所示,在电流源电路700部分为同一晶体管方式的电流源电路的情况下,从参考电流源电路404输入的电流与在各电流线CL中流过的基准电流大小相同。并且,在电流源电路700部分为电流镜方式和多栅极方式的电流源电路的情况下,从参考电流源电路404输入的电流与在CL中流过的基准电流大小可以不同。

另外,图10表示从在电流源电容721_1~721_x中没有保持电荷的状态开始通过进行一次期间TD1~TDx的动作,使规定的电荷保持在各电流源电容721_1~721_x中,使得电流源晶体管720_1~720_x流过基准电流的方法。将该方法称为统一写入方法。

另一方面,可以使用从在电流源电容721_1~721_x中没有保持电荷的状态开始,重复期间TD1~TDx的动作,一点一点在电流源电容721_1~721_x中保持电荷的方法。在该方法中,在多次重复期间TD1~TDx的动作之后,最初在各电流源电容721_1~721_x中保持规定的电荷,使得在电流源晶体管720_1~720_x中流过基准电流。将该方法称为分割写入方式。在分割写入方式中,从在各电流源电容721_1~721_x中没有保持电荷的状态开始,直到保持了规定的电荷,将重复期间TD1~TDx的次数称为分割写入方式的分割数。

分割写入方式情况下的期间TD1~TDx中各个开关(电流输入开关701_1~701_x,电流输出开关702_1~702_x,电流保持开关722_1~722_x)的状态与统一写入方式相同。但是,在分割写入方式中进行一次期间TD1~TDx所需要的时间比统一写入方式中进行期间TD1~TDx所要的时间要短。

另外,基准电流输出电路405的设定动作可以在一帧期间进行几次,也可以在数帧期间进行一次。另外,也可以一水平期间进行几次,也可以在每次重复几次水平期间进行一次。重复基准电流输出电路405的设定动作的间隔可根据基准电流输出电路具有的电流源电容721持续保持电荷的能力来进行任意选择。

另外,如图5、8、9、11所示,输入到基准电流输出电路405中的基准电流也可以是从参考电流源电路404输入的结构,也可以不设置参考电流源电路404,输入从显示装置的外部输入的一定电流来作为电流。或者,相当于图8和图9的电流源电路700的电流源电路也可处于显示装置的外部。另外,在晶体管的偏差小的情况下,在基准电流输出电路405的各个电流源电路700中也不一定进行设定动作。但是,进行了设定动作可以输出更准确的电流值。

接着,说明具有图5所示结构的像素的显示装置的驱动方法。这里,在实施形式1的结构的像素中,像素显示动作(开关部的驱动动作)和电流源电路的设定动作(像素的设定动作)也可不同步进行。即,也可进行像素的设定动作,而与开关部的端子C和端子D的导通和非导通状态无关。

另外,基准电流输出电路405的设定动作也可与像素显示动作和像素的设定动作同步进行,也可非同步进行。但是,最好图9所示的基准电流输出电路405的设定动作在不进行像素的设定动作期间进行。其原因是在图9所示的基准电流输出电路405中,在进行该设定动作的正当中不能将电流输出到电流线CLj。因此,若在各电流线CLj上配置了两个电流源电路700,在一个电流源电路将电流输出到电流线CLj期间可以对另一电流源电路进行基准电流输出电路405的设定动作。因此,可以同时进行基准电流输出电路405的设定动作和像素的设定动作。或者,作为电流源电路700_j的电路,使用电流镜电路,若构成电流镜电路的一对晶体管的一个晶体管将电流输出到电流线CLj,另一个晶体管进行基准电流输出电路405的设定动作,则可以同时进行基准电流输出电路405的设定动作和像素的设定动作。

为了简单起见,首先分别说明像素的设定动作和像素显示动作。使用图7(A)、图7(B)的定时图和图5的电路图说明图像显示动作。将信号输入到扫描线Gi,第i行的像素的选择晶体管301变为导通状态。这时,将图像信号输入到图像信号输入线S1~Sx,而将图像信号输入到第i行的各像素中。并且,在根据图像信号驱动晶体管302变为导通状态的像素中,端子D和端子C变为导通状态。通过保持电容303保持驱动晶体管302的栅极电压。即,保持驱动晶体管302的导通或非导通状态。另外这时,删除晶体管304变为非导通状态。这样,在开关部101的端子D和端子C为导通状态的像素中,从电流源电路102将像素基准电流输入到发光元件106而进行发光。

这样,选择各像素的发光状态和非发光状态,并通过数字方式表现灰度等级。作为多灰度等级的方法可以使用在每一个规定期间设定多个选择了各像素的发光或非发光状态的期间,控制选择了发光状态的时间累计的灰度等级方式(时间灰度等级方式)和将一个像素分割为多个子像素,控制选择了发光状态的子像素的面积累计的灰度等级方式(面积灰度等级方式)等。另外,也可使用公知的方法。这里作为多灰度等级的方法也可使用时间灰度等级方式。

这里,通过将删除晶体管304设为导通状态,也可使保持电容303的两个电极的电位相同,通过放电在保持电容303中保持的电荷,也可一齐将驱动晶体管302变为非导通状态。由此,在将图像信号输入到某一行的像素的正中间,也可将其他行的像素设为非发光状态。这样,可以任意设定各行像素的发光期间。

图13所示结构的开关部构成为具有选择晶体管301来作为第一开关,驱动晶体管302来作为第二开关,除此之外具有删除晶体管304。将删除晶体管304的栅极电极连接到与图像信号输入线S和扫描线G不同的布线、删除用信号线RG上。这样,删除晶体管304通过输入到删除用信号线RG上的信号,切换导通和非导通状态,而与输入到选择晶体管301和驱动晶体管302的信号无关。这样,可以将开关部的端子C和端子D间设为非导通状态,而与第一开关和第二开关的状态无关。上面是基本的图像显示动作。

接着,图7中,作为灰度等级显示方法的具体例表示使用时分割灰度等级方式情况下的驱动方法的一例。将显示一个屏幕部分的图像期间称为一帧期间F。将一帧期间F分割为多个子帧期间SF1~SFn(n为自然数)。

在第一子帧期间SF1中,选择第一行的扫描线G1,并且将栅极连接到扫描线G1的选择晶体管301变为导通状态。这里,一齐将信号输入到图像信号输入线S1~Sx。另外,这时删除晶体管304为非导通状态。根据输入到图像信号输入线S1~Sx的信号,选择第一行的各像素的驱动晶体管302的导通和非导通状态,而选择各像素的发光和非发光状态。另外,通过保持电容303保持驱动晶体管302的栅极电压。这里,为了选择各像素的驱动晶体管302的导通和非导通状态,而将输入图像信号表现为将图像信号写入到像素。

选择了导通状态的驱动晶体管302保持导通状态,直到从图像信号输入线S向驱动晶体管302的栅极输入了新的信号,或通过删除晶体管304放电保持电容303的电荷。在选择了发光状态的像素中,开关部的端子C和端子D之间变为导通状态,从电流源电路102向发光元件106输入像素基准电流而发光。并且,若终止了第一行的像素的图像信号的写入操作,马上选择对应于第二行像素的扫描线G2,而开始将图像信号写入到对应于第二行的像素上的动作。将图像信号写入到像素的动作与第一行的像素的动作相同。

对所有扫描线G1~Gy重复上述动作,而将图像信号写入到所有像素中。并将把图像信号写入到所有像素的期间记为地址期间Ta。将对应于第m(m是小于n的自然数)的子帧期间SFm的地址期间记为Tam。

写入了图像信号的像素行分别选择了发光或非发光状态。根据写入的图像信号,将各像素行发光或非发光的各像素期间记为显示期间Ts。在同一子帧期间,各像素行的显示期间Ts虽然定时不同,但是其长度完全相同。将对应于第m(m是小于n的自然数)的子帧期间SFm的显示期间记为Tsm。

在第一子帧期间SF1到第k-1(k为比n小的自然数)的子帧期间SFk-1,将显示期间Ts设定为比地址期间Ta长。在规定长度的显示期间Ts1后,开始第二子帧期间SF2。之后,对于从第二子帧期间SF2到第k-1的子帧期间SFk-1也与第一子帧期间SF1相同,操作显示装置。这里,由于多个像素行不能同时进行图像信号的写入,所以设定各子帧期间的地址期间Ta,使其各不重复。

另一方面,从第k子帧期间SFk到第n的子帧期间SFn中,将显示期间Ts设定为比地址期间Ta短。下面,详细说明第k子帧期间SFk到第n子帧期间SFn的显示装置的驱动方法。

在第k子帧期间SFk中,选择第一行的扫描线G1,并且将栅极连接到扫描线G1的选择晶体管301变为导通状态。这里,一齐将信号输入到图像信号输入线S1~Sx。另外,这时删除晶体管304为非导通状态。根据输入到图像信号输入线S1~Sx的信号,选择第一行的各像素的驱动晶体管302的导通和非导通状态,而选择各像素的发光和非发光状态。另外,通过保持电容303保持驱动晶体管302的栅极电压。在选择了发光状态的像素中,开关部的端子C和端子D之间变为导通状态,从电流源电路102向发光元件106输入像素基准电流,发光元件106发光。若终止了第一行的像素的图像信号的写入操作,接着选择对应于第二行像素的扫描线G2,而开始将图像信号写入到对应于第二行的像素上的动作。将图像信号写入到像素的动作与第一行的像素的动作相同。

对所有扫描线G1~Gy重复上述动作,而将图像信号写入到所有像素中,而终止地址期间Tak。

上述的第k子帧期间SFK的地址期间Tak的动作方法与第一子帧期间SF1到第k-1子帧期间SFK-1相同。其不同点是在终止地址期间Tak前,开始删除用信号线RG1等的选择。即,在选择了扫描线G1后,在经过了规定的期间(该期间相当于显示期间Tsk)后,选择删除用信号线RG1。并且,顺序选择删除用信号线RG1~RGy,将各像素行的删除晶体管304顺序变为导通状态,而使各行的像素顺序一律变为非发光状态。将把所有像素的删除晶体管304变为导通状态的期间记为复位期间Tr。尤其将对应于第p(p是大于k小于n的自然数)的子帧期间SFp的复位期间记为Trp。

这样,可以在将图像信号输入到某一行的像素正当中,将其他行的像素一律设为非发光状态。这样,可以自由控制显示期间Ts的长度。这里,将地址期间Tap的长度和复位期间Trp的长度设为相同。即,在写入图像信号时顺序选择各行的速度和将各行像素顺序一律设为非发光状态时的速度设为相同。由此,在同一子帧期间,虽然开始各行像素的显示期间Ts的定时不同,但是其长度全部相同。

通过将各像素行的删除晶体管304设为非导通状态,而将各像素行的像素一律设为非发光状态的期间记为非显示期间Tus。在同一子帧期间,虽然各像素行的非显示期间Tus定时不同,但其长度完全相同。尤其是将对应于第p子帧期间SFp的非显示期间记为Tusp。

在规定长度的非显示期间Tusk后,开始第k+1的子帧期间Sk+1。在第k+1的子帧期间SFk+1到第n子帧期间SFn,重复与第k子帧SFk相同的动作,而终止一帧期间F1。这里,子帧期间SF1~SFn的地址期间Ta1~Tan的长度完全相同。如上这样,使显示装置动作,并通过适当确定各子帧期间SF1~SFn的显示期间Ts1~Tsn的长度,而表现灰度等级。

接着,描述显示期间Ts1~Tsn的长度设定方法。例如,若将Ts1∶Ts2∶......∶Tsn-1∶Tsn设为20∶2-1∶......∶2-(n-2)∶2-(n-1),则可以表现2n灰度等级。作为具体例,举例在n=3的情况下,输入三比特的图像信号,来表现8灰度等级的例子。将一帧期间F分割为三个子帧期间SF1~SF3。并将各个帧期间的显示期间的长度比Ts1∶Ts2∶Ts3设为4∶21。在某一像素中,若将所有子帧期间SF1~SF3选择了发光状态时的亮度设为100%,则仅在第一子帧期间SF1选择了发光状态的情况下,表现约57%的亮度。另一方面,在仅在第二子帧期间SF2选择了发光状态的情况下,表现约29%的亮度。

另外,如上这样,不限定于在一帧期间设置与图像信号的比特数相同的子帧期间表现灰度等级的方法。例如,在一帧期间,可以通过对应于图像信号的某一比特的信号,设置多个选择发光状态和非发光状态的子帧期间。即,由多个子帧期间的显示期间的累计来表现对应于一比特的显示期间。

尤其是,通过多个子帧期间各个具有的显示期间的累计来表现对应于图像信号的高位比特的显示期间,并通过使这些子帧期间不连续出现,也可抑制假轮廓的产生。另外,各子帧期间的显示期间Ts的长度设定可以使用公知的所有方法,而不限于上述方法。

图7中,构成为第一子帧期间SF1到第n子帧期间SFn顺序出现,但是并不限于此。各子帧期间出现的顺序也可任意确定。另外,可以通过面积灰度等级方式、时分割灰度等级方式和面积灰度等级方式的组合,而不仅仅为时分割灰度等级方式,来表现灰度等级。

在本实施形式1中,虽然仅在将显示期间Ts设定为比地址期间Ta短的子帧期间中表示了设置复位期间Tr和非显示期间Tus的驱动方法,但是并不限于此。也可以是在显示期间Ts设定为比地址期间Ta长的子帧期间中,设置复位期间Tr和非显示期间Tus的驱动方法。

另外,在图13中,虽然表示了通过将删除晶体管304设为导通状态而放电保持电容303的电荷的结构,但是并不限于此。也可以是通过将删除晶体管304设为导通状态,而提高或降低与保持电容303的驱动晶体管302的栅极相连侧的电位,将驱动晶体管302设为非导通状态的结构。即,经删除晶体管304,将驱动晶体管302的栅极与输入了使驱动晶体管302为非导通状态的电位的信号的布线相连的结构。

另外,也可以不是如上那样的通过将删除晶体管304设为导通状态,使保持电容303的与驱动晶体管302的栅极相连侧的电位改变类型的结构,而可以是将删除晶体管304与驱动晶体管302串联连接,通过将删除晶体管304设为非导通状态而使开关部101的端子C和端子D间为非导通状态,而为非显示期间的结构。

除此之外,也可以自由使用关闭使用图43所说明的开关部的方法,而设置使像素一律为非发光状态的复位期间和非显示期间。

另外,也可使用设置使像素一律为非发光状态的复位期间和非显示期间,而不设置删除晶体管。

在该第一方法中,通过使保持电容的没有与驱动晶体管的栅极相连侧的电极的电位改变,而将驱动晶体管设为非导通状态的方法。图49表示其结构。将保持电容303的没有与驱动晶体管302的栅极相连侧的电极连接到布线Wco上。改变布线Wco的信号,而使保持电容303的一个电极的电位改变。这样,由于保存了在保持电容303中保持的电荷,所以保持电容303的另一个电极的电位也改变。这样,也可通过改变驱动晶体管302的栅极电位,而使驱动晶体管302为非导通状态。

第二方法是将选择了一条扫描线的期间分割为前半部分和后半部分。其特征在于在前半部分(记为栅极选择期间前半部分)中输入图像信号,在后半部分(记为栅极选择期间后半部分)中输入删除信号。这里,所谓删除信号是指在输入驱动晶体管的栅极时,将驱动晶体管设为非导通状态的信号。这样,可以设定比写入期间短的显示期间。在该方法的详细说明中,参照图49(B)说明显示装置整体的结构。显示装置具有按矩阵状配置的具有多个像素的像素部901、将信号输入到像素部901的图像信号输入线驱动电路902、第一扫描线驱动电路903A、第二扫描线驱动电路903B、切换电路904A和切换电路904B。第一扫描线驱动电路903A是在栅极选择期间的前半部分中将信号输出到各扫描线G的电路。另外,第二扫描线驱动电路903B是在栅极选择期间的后半部分中将信号输出到各扫描线G的电路。通过切换电路904A和切换电路904B,选择第一扫描线驱动电路903A与各像素的扫描线G相连,或第二扫描线驱动电路903B与各像素的扫描线G相连。图像信号输入线驱动电路902在栅极选择期间前半部分输出图像信号。另一方面,在栅极选择期间后半部分输出删除信号。

接着,参照图49(C)说明上述结构的显示装置的驱动方法。另外表示为与图7相同的部分使用同一附图标记而省略说明。在图49(C)中,将栅极选择期间991分割为栅极选择期间前半部分991A和栅极选择期间后半部分991B。在903A中,通过第一扫描线驱动电路选择各扫描线,而输入数字图像信号。进行903A的操作期间相当于写入期间Ta。另一方面,在903B中,通过第二扫描线驱动电路选择各扫描线,而输入删除信号。进行903B的操作期间相当于复位期间Tr。这样,可以设定比地址期间Ta短的显示期间Ts。另外,这里虽然在栅极选择期间后半部分输入删除信号,但是代替此也可输入下一子帧期间的数字图像信号。

第三方法是通过改变发光元件的对置电极的电位,设置非显示期间的方法。即,显示期间中设定对置电极的电位,使得其与电源线的电位之间具有规定的电位。另一方面,在非显示期间,将对置电极的电位设定为与电源线的电位大致相同。并且,在非显示期间对所有像素输入数字图像信号。即,这时,设置地址期间。这样,可以将像素设为非发光状态,而与输入到像素中的数字图像信号无关。

例如,在对置电极在所有像素中电连接的情况下,在所有像素中开始显示期间Ts的定时和终止定时相同。在规定长度的显示期间Ts后,通过将发光元件106的对置电极的电位变为再次与电源线W的电位大致相同,而将所有像素一齐设为非发光的状态。这样,可以设置非显示期间Tus。在所有像素中,非显示期间Tus的定时相同。另外,在多灰度等级化没有这种程度的要求的情况下(不需要显示期间Ts比地址期间Ta短的情况下),也可以为在所有子帧期间不设置非显示期间Tus的驱动方法。在使用该驱动方法的情况下,没有必要用删除晶体管。

另外,还可积极使用驱动晶体管302的栅极寄生电容,来代替保持电容303。同样,也可使用电流源晶体管112和电流晶体管1405的栅极寄生电容,而不配置电流源电容111。

下面对于像素的设定动作,说明下面的两种方法。

使用图6说明第一方法。图6是表示配置在图5所示的各像素中的电流源电路102的设定动作(像素的设定动作)的定时图。这里,说明接通显示装置的电源后的最初的像素设定动作。

另外,举出将像素的设定动作与图8等所示的基准电流输出电路405的设定动作同步进行的情况的例子。这里,举例为基准电流输出电路405使用图9所示的结构,以图10所示的定时图为参考,使用分割写入方式而动作的情况。另外,为简单起见,表示分割写入方式的分割数为2的情况的例子。为说明方便,表示为与图10所示的定时图动作相同的部分采用同一附图标记而省略说明。

在图6中,由SETi表示进行第i行的像素设定动作的期间。在SETi中,进行第i行的第1列到第x列的像素的设定动作。将第i行的第1列到第x列的像素设定动作分割为图6中的SETi的(1)和(2)的期间而进行说明。

首先,在SET1的期间(1)中,通过输入到信号线GN1和信号线GH1的信号,图5所示的第一行像素的电流输入晶体管1403和电流保持晶体管1404为导通状态。这时,基准电流输出电路405顺序进行图10中期间TD1~TDx所示的动作,顺序决定在各电流线CL1~CLx中流过的电流。这时,确定电流I0’,使其在电流线CL1~CLx中流过。另外,这里,基准电流输出电路405也可使用分割写入方式进行设定动作。因此,仅通过进行一次期间TD1~TDx示的动作,而不充分进行设定动作。因此,若将基准电流设为I0,则电流值I0’<I0。

接着,说明在各电流线CL1~CLx中流过电流I0’后的各像素的电源线电路102的动作。例如,在第一行第j列的像素的情况下,若终止期间TDj,则进行设定,使得在电流线CLj上流过电流I0’。由此,在第j列的像素的电流晶体管1405中流过电流I0’。这里,第一行像素的电流晶体管1405的栅极与漏极端子经为导通状态的电流保持晶体管1404而连接。因此,电流晶体管1405在栅和源极间电压(栅极电压)和源和漏极间电压相等的状态下,即饱和区域中动作,而流过漏极电流。第一行j列的像素的电流晶体管1405中流过的漏极电流决定为在电流线CLj中流过的电流I0’。这样,电流源电容111保持电流晶体管1405流过电流I0’时的栅极电压。

若到期间TD1~TDx终止,并且电流源电容721_x结束保持对应于在电流线CL中流过的电流I0’的电荷,则进入到期间(2)。在期间(2)中,改变信号线GH1的信号,而将电流保持晶体管1404变为非导通状态。由此,在第一行的像素的电流源电容111中保持电荷。

另外,图中由TQ1所示的期间相当于从电流线CLx向第一行x列的像素的电流源电路102的电流晶体管1405输入电I0’,使电荷保持在电流源电容111中的期间。图中由TQ1所示的期间比在电流晶体管1405中流过的电流变为稳定状态所需要的时间短的情况下,在电流源电容11中不充分保持电荷。但是,这里为简单起见,将TQ1设定为充分长。

这样,进行第一行的各像素的设定动作。这里,在各像素的电流源电路102中,电流晶体管1405和电流源晶体管112的栅极电位相等。电流晶体管1405和电流源晶体管112的源极端子的电位相等。另外,最好电流晶体管1405和电流源晶体管112的电流特性相等。为了简单起见,这里,设电流晶体管1405和电流源晶体管112的电流特性相等。因此,若对电流源电路102的端子A和端子B间施加电压,则在电流源晶体管112中流过根据在电流晶体管1405中流过的电流I0’的一定电流。

在使用分割写入方式的基准电流输出电路405的显示装置中,接通显示装置的电源后的初始SET1的电流线CL1~CLx中流过的电流I0’为未达到基准电流的值。因此,可以不充分进行该SET1期间的像素的设定动作。即,在接通显示装置的电源之后的第一行的像素设定动作中,不会在第一行的像素所分别具有的电流源电路102的电流源电容111中保持对应于基准电流的电压(像素对应基准电压)。

接着在SET2的期间(1)中,通过输入信号线GN2和信号线GH2的信号,第二行的像素的电流输入晶体管1403和电流保持晶体管1404为导通状态。同时输入信号线GN1的信号变化,第一行的像素的电流输入晶体管1403为非导通状态。这样,第一行的像素的电流晶体管1405和电流源晶体管112的栅极电压仍保持,电流线CL1和电流晶体管1405的连接被切断。

在SET2的期间(1)中,基准电流输出电路405顺序进行在图10中期间TD1~期间TDx所示的动作,顺序确定流向各电流线CL1~CLx的电流。此时,通过在前面的SET1期间的期间TD1~TDx中进行的动作,基准电流输出电路711的电流源电容721_1~721_x中保持现有程度的电荷。进行SET2的期间TD1~TDx的动作时,接入显示装置的电源后,反复2次期间TD1~TDx的动作。

这里,将分割写入方式的分割数设为2,因此SET2的期间TD1~TDx结束后,基准电流输出电路405的电流源电容721_1~721_x中保持电流源晶体管720_1~720_x流过基准电流I0的电荷。这样,流过各电流线CL1~CLx的电流确定为基准电流I0。

如此,接入显示装置的电源后的初始的SET2中,将由基准电流输出电路405确定的流过电流线CL1~CLx的电流值确定为基准电流I0。即,接入显示装置的电源后的初始的SET2中,充分进行基准电流输出电路405的设定动作。

接着,说明向各电流线CL1~CLx流过基准电流I0后的各像素的电流源电路的动作。例如,第二行第j列的像素的情况下,期间TDj结束时,设定为向电流线CLj流过基准电流I0。这样,第j列的像素的电流晶体管1405中流过基准电流I0。第二行的像素的电流晶体管1405的栅极与漏极端子经变为导通状态的电流保持晶体管1404连接。因此,电流晶体管1405在栅极和源极间电压(栅极电压)与源极和漏极间电压相等的状态,即饱和区域动作,流过漏极电流。流过第二行第j列的像素的电流晶体管1405的漏极电流确定为流过电流线CLj的基准电流I0。这样,电流源电容111保持电流晶体管1405流过基准电流I0时的栅极电压。

直到期间TD1~TDx结束,电流源电容721_x结束保持与流过电流线CL的基准电流I0对应的电荷后,进入期间(2)。期间(2)中,信号线GH2的信号变化,电流保持晶体管1404为非导通状态。由此,第二行的像素的电流源电容111中保持电荷。

图中TQ2所示期间相当于从电流线CLx向第二行x列的像素的电流源电路102的电流晶体管1405输入基准电流I0、电流源电容111中保持电荷的期间。当图中TQ2所示期间比流过电流晶体管1405的电流变为恒定状态所需要的时间短时,电流源电容111中不充分保持电荷。即,像素的设定动作不充分进行。这里为了简单,将TQ2设定得非常长。

这样,进行第二行的各像素的设定动作。各像素的电流源电路102中,电流晶体管1405和电流源晶体管112的栅极电位相等。电流晶体管1405和电流源晶体管112的源极端子的电位相等。希望电流晶体管1405和电流源晶体管112的电流特性相等。为了简单,设电流晶体管1405和电流源晶体管112的电流特性相等。因此,电流源电路102的端子A和端子B之间施加电压时,电流源晶体管112的源极和漏极之间流过对应流过电流晶体管1405的基准电流I0的恒定电流(像素基准电流)。

SET2结束后,输入信号线GN2的信号变化,第二行的像素的电流输入晶体管1403为非导通状态。这样,第二行的像素的电流晶体管1405和电流源晶体管112的栅极电位仍保持,切断电流线CL2和电流晶体管1405的连接。

对全部的行反复进行与SET2相同的动作。其中,基准电流输出电路405的设定动作在SET2中已经结束。因此,SET3以后的动作中,在SETi的期间(1)间继续向全部电流线CL1~CLx流过基本与基准电流相等的电流。一旦基准电流输出电路405的设定动作结束后,重新开始SETi的期间(1),在第i行的全部像素的电流源电容111中同时进行保持像素对应基准电压的动作。

这样,在SET2结束的时刻,基准电流输出电路405具有的各电流源电容721_1~721_x中保持向各电流线CL1~CLx流过基准电流I0的电荷。这样,在SET3以后的期间TD1~TDx中,进行重新保持电流源电容721_1~721_x的电荷放电的大小的动作。SET2以后流向各电流线CL1~CLx的电流基本确定为基准电流,像素的设定动作充分进行(完成)。

进行SET1~SETy的动作后,结束像素设定的第一帧期间。一次一次地选择全部信号线GN1~GNx和信号线GH1~GHx,将进行一次全部像素的设定动作的期间叫做像素设定的1帧期间。

结束像素设定的第一帧期间后,开始像素设定的第二帧期间。在像素设定的第二帧期间也反复进行和像素设定的第一帧期间同样的动作。在像素设定的第一帧期间中,第一行的像素设定动作未充分进行。但是,在像素设定的第二帧期间完成基准电流输出电路405的设定动作。因此,通过在像素设定的第二帧期间进行SET1的动作,也可充分进行第一行的像素的设定动作。这样,全部的像素的设定动作充分进行(完成)。

在图6的定时图中,基准电流输出电路405的分割数设为2,但不限定于此,可为任意数。假设分割数比显示装置具有的像素行数大的情况下,接入显示装置的电源后的第一次(像素设定的第一帧期间)的像素的设定动作对全部像素行不充分进行。但是通过多次反复像素的设定动作可充分进行像素的设定动作。可以是像素设定的第一帧期间哪个像素的设定动作都不充分进行,而在像素设定的第二帧期间以后完成全部像素的设定动作。

例如,可使用将各设定期间SETi的期间(1)的长度设定得短、通过多次进行SET1~SETy的动作,慢慢进行像素的设定动作的方法。表示出接入显示装置的电源后的基准电流输出电路405的设定动作和像素的设定动作同时开始的例子,但可以是在充分进行基准电流输出电路405的设定动作后进行像素的设定动作。

一旦像素的设定动作完成后,为了重新充电由于泄漏电流等保持在电流源电容111中的电荷减少的部分而进行像素的设定动作。其定时根据电流源电容111的放电速度等有各种形式。一旦像素的设定动作完成后再次进行像素的设定动作中,由于可仅充电保持在电流源电容111中的电荷放电的大小,相对开始的像素的设定动作,其以后的像素的设定动作可缩短在向各像素输入基准电流后到变为恒定状态之前的时间。因此,相对于第一次的像素的设定动作,其以后的像素的设定动作可将向信号线GN、信号线GH输入信号的驱动电路和基准电流输出电路405的驱动频率设定得更高。

接着,使用图15说明像素的设定动作的第二方法。图15是表示图5所示的各像素上配置的电流源电路102的设定动作(像素的设定动作)的定时图。图15(a)中举例说明在1帧期间的前半和后半期间进行像素的设定动作和图8等所示的基准电流输出电路405的设定动作的情况。这里,举例说明基准电流输出电路405使用图9所示的结构,以图10所示的定时图为参考动作的情况。进行与图10所示的定时图相同的动作的部分使用相同附图标记表示,而省略说明。

首先,1帧期间的前半期间中,基准电流输出电路405顺序进行图10中期间TD1~TDx所示的动作,顺序确定流向各电流线CL1~CLx的电流。接着,对于在1帧期间的后半期间的各像素的电流源电路102的动作,说明第一行像素的情况。通过基准电流输出电路405的设定动作,全部电流线CL设定为流过基准电流。这里,第一行的像素的电流晶体管1405的栅极和漏极端子经变为导通状态的电流保持晶体管1404连接。因此,电流晶体管1405在栅极和源极间电压(栅极电压)与源极和漏极间电压相等的状态(饱和区域)下动作,流过漏极电流。流过第一行第j列的像素的电流晶体管1405的漏极电流确定为流过电流线CLj的基准电流。这样,电流源电容111保持电流晶体管1405流过基准电流时的栅极电压。接着信号线GH1的信号变化,电流保持晶体管1404为非导通状态。由此,第一行的像素的电流源电容111保持电荷。

这样,进行第一行的各像素的设定动作。各像素的电流源电路102中,电流晶体管1405和电流源晶体管112的栅极电位相等、电流晶体管1405和电流源晶体管112的源极端子的电位相等。希望电流晶体管1405和电流源晶体管112的电流特性相等。为了简单,假定电流晶体管1405和电流源晶体管112的电流特性相等。因此,电流源电路102的端子A和端子B之间施加电压时,电流源晶体管112流过对应流过电流晶体管1405的基准电流的恒定电流。

接着通过输入信号线GN2和信号线GH2的信号,第二行的像素的电流输入晶体管1403和电流保持晶体管1404为导通状态。同时输入信号线GN1的信号变化,第一行的像素的电流输入晶体管1403为非导通状态。这样,第一行的像素的电流晶体管1405和电流源晶体管112的栅极电位仍保持,切断电流线CL1和电流晶体管1405的连接。在第二行的像素中与第一行时同样进行像素的设定动作。接着对第三行的像素、第四行的像素顺序反复同样动作。对全部的行结束像素的设定动作后,结束1帧期间。进入下一帧期间后,同样前半期间进行基准电流输出电路405的设定动作,后半期间进行像素的设定动作。一旦像素的设定动作完成后,为重新充电由于泄漏电流等保持在电流源电容111中的电荷减少的部分而进行像素的设定动作。其定时根据电流源电容111的放电速度等有各种形式。

同样一旦基准电流输出电路405的设定动作进行后,为重新充电电容721中保持的电荷减少的的大小而进行设定动作。定时为各种各样,像素和基准电流输出电路405的设定动作可与图像的显示动作毫无关系地动作。图7的地址期间Ta和显示期间Ts、非显示期间Tus可毫无关系地动作。其理由是像素和基准电流输出电路405的设定动作与图像的显示动作不对彼此的动作产生影响。因此,替代如图15(a)可按图15(b)进行设定动作。图15(b)中,信号线驱动电路不动作的期间进行基准电流输出电路405的设定动作,剩余期间进行像素的设定动作。这样,可完全按任意次数和定时进行设定动作。像素的设定动作不需要1行1行地顺序进行,基准电流输出电路405的设定动作也不需要1行1行地顺序进行。

在电流保持晶体管1404的源极端子和漏极端子的未与电流晶体管1405和电流源晶体管112的栅极连接的侧直接连接电流线CL的结构中,为向全部的像素的电流输入晶体管1403为非导通状态时的电流线CL提供一定电位的结构。该一定电位设定为在显示装置具有的多个像素中在这些电流源电容111中保持像素对应基准电压时的电流晶体管1405的栅极电位的平均程度。这样,电流保持晶体管1404的源极和漏极端子之间的电压减小,由电流保持晶体管1404的泄漏电流可抑制储存在电流源电容111中的电荷的放电。为向电流线CL中提供一定电位或流过基准电流的切换在基准电流输出电路405中进行的结构。

通过对电流晶体管1405的栅极长宽比改变电流源晶体管112的栅极长宽比可对基准电流值改变像素基准电流的值。例如,将基准电流设定为大于像素基准电流,则像素的设定动作中,可缩短电流源电容111保持像素对应基准电压之前所需的时间,而可降低噪声的影响。

配合与电流线CL1~CLx对应的各像素的发光元件的特性,可确定多个不同的电流值的基准电流。例如,可改变并设定设置发红光、发绿光和发蓝光的不同发光色的发光元件的各像素的各自的电流线CL中流过的基准电流的电流值。由此,可对3色的发光元件的发光亮度进行平衡。3色的发光亮度的平衡处理方法可通过改变点亮期间的长度进行,还可与改变输入对应各色的像素的基准电流的电流值组合。或者可以由电流晶体管1405和电流源晶体管112按色改变栅极长宽比。

接着,说明图像显示动作和像素的设定动作的关联。开始图像显示动作和像素的设定动作的定时有各种各样。

1个是在一旦全部的像素的设定动作充分完成后进行接入显示装置的电源后的最初的图像显示动作的方法。该情况下,从最初的图像显示动作开始通过图像信号选择发光状态的像素的发光元件按规定亮度发光。

其他方法是边进行像素的设定动作边同时进行接入显示装置的电源后的最初的图像显示动作的方法。该情况下,到完成像素的设定动作之前的期间中进行的图像显示动作中,通过图像信号选择了发光状态的像素的发光元件的发光亮度达不到规定亮度。因此,正确的灰度等级显示在对全部像素的设定动作充分完成后才开始。

图5所示的像素部的结构中,信号线GN、信号线GH、扫描线G、删除用信号线RG等考虑驱动的定时等可共用。例如,可共用信号线GHi和信号线GNi。将电流保持晶体管1404设为非导通状态的定时和将电流输入晶体管1403设为非导通状态的定时完全相同,在像素的设定动作上没有问题。

(实施形式2)

本实施形式中,图12表示同一晶体管方式的电流源电路的结构例子。这里主要说明与实施形式1不同的部分,重复部分省略说明。因此,图12中与图3相同部分用相同附图标记表示。

图12中,电流源电路102由电流源电容111、电流源晶体管112、电流输入晶体管203、电流保持晶体管204、电流停止晶体管205、电流线CL、信号线GN、信号线GH、信号线GS构成。表示出电流源晶体管112为p沟道型的例子。在电流源晶体管112为n沟道型时,也根据图3(C)所示结构,容易应用。该情况下的例子在图24表示。与图12相同的部分用相同附图标记表示。

图12中,电流输入晶体管203、电流保持晶体管204、电流停止晶体管205为n沟道型,但由于单单作为开关动作,为p沟道型也无妨。其中图12中,电流保持晶体管204连接于电流源晶体管112的栅极和漏极之间的情况下,希望电流保持晶体管204为p沟道型。其理由是为n沟道型的情况下,端子B的电位有时变得非常低,此时电流保持晶体管204的源极电位也非常低。其结果是电流保持晶体管204可能难以为非导通状态。与此不同,电流保持晶体管204为p沟道型时没有这种担心。

电流源晶体管112的栅极和电流源电容111的一个电极连接。电流源电容111的另一个电极与电流源晶体管112的源极端子连接。电流源晶体管112的源极端子连接电流源电路102的端子A。电流源晶体管112的栅极和漏极端子经电流保持晶体管204的源极和漏极端子之间而连接。电流保持晶体管204的栅极连接信号线GH。电流源晶体管112的漏极端子和电流线CL经电流输入晶体管203的源极和漏极端子之间而连接。电流输入晶体管203的栅极连接信号线GN。电流源晶体管112的漏极端子经电流停止晶体管205的源极和漏极端子之间而与端子B连接。电流停止晶体管205的栅极连接信号线GS。

上述结构中,电流源晶体管112的栅极可不经电流输入晶体管203的源极和漏极端子之间而连接电流线CL。即,电流保持晶体管204的源极端子和漏极端子的不与电流源晶体管112的栅极连接的那侧直接连接电流线CL的结构也可。此时,通过调整电流线CL的电位,可减小电流保持晶体管204的源极和漏极间电压。其结果是电流保持晶体管204为非导通状态时,可减小电流保持晶体管204的泄漏电流。不限定于此,可连接成电流保持晶体管204为导通状态时,电流源晶体管112的栅极电位与电流线CL的电位相等。即,像素的设定动作时,为图62(a)那样,发光时如图(b)那样。如此,可连接布线和开关。因此,电流源电路的结构为图72所示。

电流保持晶体管204的源极端子和漏极端子的不与电流源晶体管112的栅极连接的那侧直接连接电流线CL的结构中,构成为向全部像素的电流输入晶体管203为非导通状态时的电流线CL提供一定电位。该一定电位设定为在显示装置具有的多个像素中在这些电流源电容111中保持像素对应基准电压时的电流源晶体管112的栅极电位的平均程度。这样,电流保持晶体管204的源极和漏极端子之间的电压减小,由电流保持晶体管204的泄漏电流可抑制储存在电流源电容111中的电荷的放电。

可以是向电流线CL中提供一定电位或流过基准电流的切换在基准电流输出电路405中进行的结构。电流保持晶体管204连接在电流源晶体管112的栅极和电流线CL之间的情况下,电流保持晶体管204的极性可以是任何极性。由于电流保持晶体管204为n沟道型电流线CL的电位不会过低,因此电流保持晶体管204难以变为非导通状态。

作为开关部的结构,与实施形式1中说明的同样,可使用各种结构。作为一个例子,为与图13所示的同样结构,省略说明。

图14表示具有图12所示的结构的电流源电路102和图13所示的结构的开关部101的像素100按矩阵状配置的像素区域的一部分的电路图。图14中,仅代表性地表示出第i行第j列、第(i+1)行第j列、第i行第(j+1)列、第(i+1)行第(j+1)列的4像素。图12和图13相同的部分用相同附图标记表示,省略说明。对应第i行、第(i+1)行的各自的像素行的扫描线表示为Gi,Gi+1、删除用信号线表示为RGi,RGi+1、信号线GN表示为GNi,GNi+1、信号线GH表示为GHi,GHi+1、信号线GS表示为GSi,GSi+1。对应第j列、第(j+1)列的各自的像素列的图像信号输入线S表示为Sj,Sj+1、电源线W表示为Wj,Wj+1、电流线CL表示为CLj,CLj+1、布线Wco表示为Wcoj,Wcoj+1。从像素区域外部向电流线CLj,CLj+1输入基准电流。

发光元件106的像素电极连接端子D,对置电极被施加对置电位。图14中,表示出将发光元件的像素电极作为阳极、将对置电极作为阴极的结构。即,表示出电流源电路的端子A连接电源线W,端子B连接开关部101的端子C的结构。但是,在发光元件106的像素电极为阴极、对置电极为阳极的结构的显示装置中,也容易应用本实施形式2的结构。下面在图50中表示出在图14所示结构的像素中将发光元件106的像素电极作为阴极、对置电极变为阳极的例子。图50中,与图14相同的部分使用相同附图标记表示,省略说明。

图14中,电流源晶体管112为p沟道型。另一方面,图50中,电流源晶体管112为n沟道型。这样,可使流过的电流方向为相反方向。此时,图50的端子A连接开关部的端子C,端子B连接电源线W。

图14和图50中,驱动晶体管302仅用作开关功能,因此n沟道型和p沟道型都无所谓。但是,驱动晶体管302最好在其源极端子的电位被固定的状态下动作。因此如图14所示的发光元件106的像素电极为阳极、对置电极为阴极的结构中,驱动晶体管302最好为p沟道型。另一方面,图50所示的发光元件106的像素电极为阴极、对置电极为阳极的结构中,驱动晶体管302最好为n沟道型。图14中,由于各像素的布线Wco和电源线W可以保持在相同电位,因此可共用。不同的像素间的布线Wco之间、电源线W之间、布线Wco和电源线W都可共用。

图14所示的像素部的结构中,信号线GN、信号线GH、信号线GS、扫描线G、删除用信号线RG等考虑驱动的定时等可共用。例如可共用信号线GHi和信号线GNi。此时,电流输入晶体管203为非导通状态的定时和电流保持晶体管204为非导通状态的定时完全相同,像素的设定动作上没有问题。另外的例子是可共用信号线GSi和信号线GNi。此时,使用与电流输入晶体管203的极性不同极性的电流停止晶体管205。这样,电流输入晶体管203的栅极和电流停止晶体管205的栅极中输入相同信号时,一个晶体管可为导通状态,另一个晶体管可为非导通状态。而且,可共用删除用信号线RG和信号线GS。

而且,替代布线Wco和布线Wi,可使用其他像素行的扫描线。这在不进行图像信号的写入期间利用扫描线的电位保持为一定电位的像素行。例如替代电源线而使用1个之前的像素行的扫描线Gi-1。但是,该情况下,考虑扫描线G的电位,需要注意选择晶体管301的极性。

将电流停止晶体管205和删除晶体管304汇总为一个,可省去其中一个。像素的设定动作时,若向驱动晶体管302和发光元件106中泄漏电流,则不能进行正确设定。因此,像素的设定动作时,可以是电流停止晶体管205为非导通状态或者为了驱动晶体管302为非导通状态而将删除晶体管304设为导通状态之一。当然也可对二者都进行设定。另一方面,在非显示期间中,同样可将电流停止晶体管205设为非导通状态或将删除晶体管304设为导通状态。从以上可知,可省略电流停止晶体管205或删除晶体管304之一。

具有上述结构的开关部和电流源电路的像素中,共用各布线的具体例子在图73表示。图73(A)~(F)中,信号线GN和信号线GH共用,布线Wco和电源线W共用。为省略电流停止晶体管205的结构。尤其图73(A)中,电流保持晶体管204的源极端子或漏极端子中,将不与电流源电容111的一个电极连接的侧直接连接电流线CL。图73(B)中,删除晶体管304串联连接电流源晶体管112和驱动晶体管302。图73(D)中,为电源线W顺序经开关部101的驱动晶体管302、电流源电路102的电流源晶体管112连接发光元件106的结构。该结构中,设置追加晶体管290。通过追加晶体管290连接电源线W和电流源晶体管112的源极端子,使得在开关部关的状态下,即驱动晶体管302为非导通状态下可进行像素的设定动作。图73(E)中,为电流源晶体管112是n沟道型的结构。此时,电流保持晶体管204的源极端子或漏极端子中,将不与电流源电容111的一个电极连接的侧直接连接电源线W。图73(F)中,是在图73(D)中将电流源晶体管112设为n沟道型的结构。这样,布线共用、晶体管的共用、极性、位置、开关部与电流源电路的位置、开关部和电流源电路的结构等可进行各种变化,另外,通过改变组合方式可容易实现各种电路。

说明具有图14所示的结构的像素的显示装置的驱动方法。说明中使用图16。关于基准电流输出电路405和参照电流源电路404的结构和动作,与实施形式1中说明的同样。因此省略说明。

首先关于像素显示动作,与实施形式1中使用图7说明的同样。不同的是关于电流停止晶体管205的动作。存在电流停止晶体管205的情况下,点亮期间中电流停止晶体管205必须为导通状态。这是因为如果电流停止晶体管205为非导通状态,则即便例如驱动晶体管302为导通状态也不会向发光元件流过电流。因此,点亮期间中需要电流停止晶体管205为导通状态。非点亮期间中任何状态都可以。除以上这一点,都与实施形式1同样,因此省略详细说明。

接着描述像素的设定动作。如实施形式1那样,图5所示结构的显示装置,将电流镜方式用作像素的电流源电路的情况下,非同步进行图像显示动作和像素的设定动作。另一方面,本实施形式2中,在图14所示的结构的显示装置,即像素的电流源电路使用同一晶体管方式的情况下,希望图像显示动作和像素的设定动作同步。

各像素中进行像素的设定动作时,为在电流源电容111中保持像素对应基准电压,需要设定流过电流线CL的基准电流为电流源晶体管112的漏极电流的状态。因此,如果进行像素的设定动作期间,流过电流源晶体管112的电流的一部分从电流源电路102流向发光元件106,则电流源晶体管112的漏极电流与流过电流线CL的基准电流为不同值,不能正确地在电流源电容111中保持像素对应基准电压。为防止这一点,进行像素的设定动作期间,需要不向该像素的发光元件流过电流。

因此,进行像素的设定动作期间,不能进行图像的显示。这样,像素的设定动作设置不进行图像显示动作的期间、图像显示动作中不进行图像显示的期间等,需要在该期间进行该设定动作。也就是,希望图像显示动作和像素的设定动作同步进行。

图14所示的结构的显示装置中,各像素中在电流源晶体管112与电流线CL电连接期间,将电流停止晶体管205设为非导通状态。这样即便开关部的端子C和端子D为导通状态,也为发光元件106中不输入电流的状态,正确进行像素的设定动作。

或者图14所示的结构的显示装置中,仅各像素的开关部的端子C和端子D之间,即驱动晶体管302为非导通状态时,可进行该像素的设定动作。此时,不需要设置电流停止晶体管205。即,为电流源晶体管112的漏极端子直接连接端子B的结构。驱动晶体管302为非导通状态可等同于删除晶体管304为导通状态。即,仅非点亮期间进行像素的设定动作时不需要设置电流停止晶体管205。

接着表示出何时进行像素的设定动作的例子。大概而言,有2个时间。一个是在显示期间进行像素设定动作的情况下。但是该情况下,像素设定动作中不发光。因此为显示期间中插入不发光期间的形式。即便像素设定动作结束,如果图13的保持电容303的电容保持的信号没有变化,则可快速再开始显示动作。另一个是图像显示动作的非显示期间Tus中进行像素的设定动作的方法。该情况下,发光元件不发光,因此可容易进行像素设定动作。接着关于像素设定动作,说明在哪几个期间完成全部的像素的设定动作。例如描述2个情况。一个是在1帧期间结束全部像素的设定动作的情况。另一个是在1帧期间结束1行的像素的设定动作的情况。该情况下,花费多个帧期间后渐渐结束全部像素的设定动作。首先详细说明第一种情况。

说明中使用图16的定时图。与图7的定时图同样动作的期间使用相同附图标记表示。为了简单,使用1帧期间分割为3个子帧期间SF1~SF3的例子。以子帧期间SF3中,需要设定比地址期间Ta3短的显示期间Ts3、设置复位期间Tr3和非显示期间Tus3的驱动方法为例。并且非显示期间Tus3中进行像素的设定动作。

图16(A)中,第一子帧期间SF1和第二子帧期间SF2中不设置非显示期间Tus,因此不进行像素的设定动作。另一方面,与开始第三子帧期间SF3的复位期间Tr3同时,进行第一行像素的设定动作。进行第k行的像素的设定动作的期间用SETk表示。并且SET1结束后,开始SET2,进行第二行像素的设定动作。结束SET1~SETy后,对全部像素结束像素的设定动作。这样,SET1~SETy的动作在复位期间Tr3中进行。以后的帧期间中可反复同样动作。但是,不需要按每帧期间进行像素的设定动作。可根据像素的电流源电容的保持能力确定。

图16(B)是详细表示图16(A)的第三子帧期间SF3的复位期间的动作的定时图。如图16(B)的图像显示动作所示,可与复位期间Tr3的删除用信号线RG1~RGy的扫描同步进行SET1~SETy。这样,与删除用信号线RG1~RGy的扫描同步进行SET1~SETy的情况下,图14所示的信号线GN1~GNy、信号线GH1~GHy和信号线GS1~GSy的频率与删除用信号线RG1~RGy的信号的频率可相同。因此,向这些信号线(删除用信号线RG1~RGy、信号线GN1~GNy、信号线GH1~GHy和信号线GS1~GSy)输入信号的驱动电路全部或部分可共用。

这里如图16(B)所示,与删除用信号线RG1~RGy的扫描同步进行SET1~SETy的情况下,脉冲输出电路711输出的采样脉冲的频率与向像素的图像信号输入线S1~Sx输入信号的信号线驱动电路的频率可相同。如此,可部分共用信号线驱动电路和基准电流输出电路405。

接着说明1帧期间中在1行像素中进行像素的设定动作的情况。说明中使用图40。与图7的定时图同样动作的期间用相同附图标记表示。图40(A)是表示第一帧期间F1的动作的定时图。图40(B)是表示第i帧期间Fi的动作的定时图。

图40(A)中第一子帧期间SF1和第二子帧期间SF2中不设置非显示期间Tus,因此不进行像素的设定动作。另一方面,与开始第三子帧期间SF3的复位期间Tr3同时,开始SET1,而进行第一行像素的设定动作。这样,SET1的动作在第一行的像素的非显示期间Tus1中使用全部的Tus1的期间进行。接着第二帧期间F2开始,进行第二行像素的设定动作。以后进行同样动作。

例如进行第i行像素的像素设定动作时的动作使用图40(B)来说明。第i行像素的设定动作在第i帧Fi中进行。第i帧Fi中同样也是在第一子帧期间SF1和第二子帧期间SF2中不设置非显示期间Tus,因此不进行像素的设定动作。另一方面,开始第三子帧期间SF3的复位期间Tr3,与开始第i行的像素的非显示期间Tusi同时,开始SETi,进行第i行像素的设定动作。这样,SETi的动作在第i行的像素的非显示期间Tusi中使用全部的Tusi的期间进行。第一帧期间F1~第y帧期间Fy结束后,对全部像素终止像素的设定动作。以后的帧期间可反复同样动作。但是,不需要按每帧期间进行像素的设定动作。可根据像素的电流源电容的保持能力确定。

这样,1帧期间进行1行的像素的设定动作的情况下,有可正确进行像素的设定动作的优点。即,进行像素的设定动作的期间长,因此可充分进行设定动作。因此,即便基准电流的大小小时,也可正确地进行设定动作,通常,若基准电流的大小小,由于布线的交叉电容等充电需要时间,因此难以正确地进行设定动作。但是,如果设定动作的期间设定得长,则可正确进行设定动作。如果必须在一帧期间对所有行像素进行设定动作的情况下,1行的像素的设定时间缩短了。因此难以进行正确设定。如果像实施方式1那样,像素的电流源电路为电流镜面的方式,则可将基准电流的大小设定得大,因此即便缩短像素的设定时间也容易进行正确设定。另一方面,像本实施方式那样,像素的电流源电路是同一晶体管方式的情况下,由于不能将基准电流的大小设得大,因此难以进行正确设定。因此将设定期间设置得长是有效的。这样,通过图16和图40所示的驱动方法可同步进行像素的设定动作和图像显示动作。

图16和图40中,表示出仅1帧期间的1个子帧期间中设置非显示期间时的驱动方法,但本发明的显示装置的驱动方法不限定于此。1帧期间的多个子帧期间中设置非显示期间时的驱动方法也可使用。此时,也可以是在1帧期间的全部的多个子帧期间中的非显示期间Tus中进行像素的时的动作的驱动方法。可以是仅在1帧期间的的多个子帧期间中的几个非显示期间Tus中进行像素的设定动作的驱动方法。

全部的像素的设定动作一旦完成后,反复像素的设定动作的定时可根据像素的电流源电路具有的电流源电容的电荷保持能力任意设定。即,多帧期间有根本不进行设定动作的期间。

这里,简单叙述某行的像素的设定动作。例如,关注第一行像素。首先,通过输入信号线GN1和信号线GH1的信号使图14所示的第一行的像素的电流输入晶体管203和电流保持晶体管204为导通状态。通过信号线GS1的信号第一行像素的电流停止晶体管205为非导通状态。在没有电流停止晶体管205的情况下,通过使删除晶体管304为导通状态等可将驱动晶体管302设为非导通状态。

并且,向电流线CL流入基准电流。这样,向像素的电流源晶体管112流过基准电流。这里,第一行像素的电流源晶体管112的栅极和漏极端子经导通状态的电流保持晶体管204连接。因此,电流源晶体管112在栅极和源极间电压(栅极电压)与源极和漏极间电压相等的状态,即饱和区域下动作,流过漏极电流。流过第一行的像素的电流源晶体管112的漏极电流确定为流过电流线CL的基准电流。这样,电流源电容111保持电流源晶体管112流过基准电流时的栅极电压。其间,电流停止晶体管205为非导通状态。由此,没有基准电流泄漏。

接着信号线GH1的信号变化,电流保持晶体管204为非导通状态。由此,第一行像素的电流源电容111保持电荷。之后,信号线GN1的信号变化,第一行像素的电流输入晶体管203为非导通状态。这样,第一行像素的电流源晶体管112仍保持栅极电压,切断与电流线CL1的连接。随后,信号线GS1的信号变化,电流停止晶体管205可为导通状态,也可仍为非导通状态。点亮期间中可为导通状态。

这样,进行第一行的各像素的设定动作。由此,以后在各像素的电流源电路102中,在端子A和端子B之间施加电压时,电流源晶体管112的源极和漏极之间流过与基准电流相同大小的电流。

(实施形式3)

本实施形式中,说明多栅方式的电流源电路。这里,主要说明与实施形式1和实施形式2不同的部分,相同部分省略说明。

使用图57说明多栅方式1的电流源电路。与图3相同部分使用相同附图标记表示。多栅方式1的电流源电路具有电流源晶体管112和电流停止晶体管805。具有用作开关功能的电流输入晶体管803、电流保持晶体管804。这里,电流源晶体管112、电流停止晶体管805、电流输入晶体管803、电流保持晶体管804可以是p沟道型,也可以是n沟道型。但电流源晶体管112和电流停止晶体管805需要是同极性的。这里,表示出电流源晶体管112和电流停止晶体管805是p沟道型的例子。希望电流源晶体管112和电流停止晶体管805电流特性相等。另外,具有保持电流源晶体管112的栅极电位的电流源电容111。具有向电流输入晶体管803的栅极输入信号的信号线GN和向电流保持晶体管804的栅极输入信号的信号线GH。另外具有输入控制信号的电流线CL。电流源电容111通过利用晶体管的栅极电容等可省略。

电流源晶体管112的源极端子连接端子A。电流源晶体管112的栅极和源极端子经电流源电容111连接。电流源晶体管112的栅极和源极端子经电流源电容111相连。电流源晶体管112的栅极和电流停止晶体管805的栅极连接,经电流保持晶体管804连接电流线CL。电流源晶体管112的漏极端子和电流停止晶体管805的源极端子连接,经电流输入晶体管803连接电流线CL。电流停止晶体管805的漏极端子和端子B连接。

图57(A)中,改变电流保持晶体管804的配置,也可为图57(B)所示电路结构。图57(B)中,电流保持晶体管804连接在电流源晶体管112的栅极和漏极端子之间。

接着说明上述多栅方式1的电流源电路的设定方法。图57(A)和图57(B)中,其设定动作同样。这里以图57(A)所示电路为例说明其设定动作。说明中使用图57(C)~57(F)。多栅方式1的电流源电路中,顺序经过图57(C)~57(F)的状态来进行设定动作。为说明简单将电流输入晶体管803、电流保持晶体管804表示为开关。这里,表示出设定电流源电路的控制信号为控制电流的例子。

图57(C)所示的期间TD1中,电流输入晶体管803、电流保持晶体管804为非导通状态。此时,电流停止晶体管805为非导通状态。这是因为通过导通状态的电流保持晶体管804和电流输入晶体管803将电流停止晶体管805的源极端子和栅极的电位保持相等。即,如果将源极和栅极间电压为零时为非导通状态的晶体管用于电流停止晶体管805,则期间TD1中可自动将电流停止晶体管805设为非导通状态。这样,通过从未示出的路径流过电流,在电流源电容111中保持电荷。

图57(D)所示的期间TD2中,由于保持的电荷,电流源晶体管112的源极和栅极间电压为阈值电压以上。这样,向电流源晶体管112流过漏极电流。

图57(E)所示的期间TD3中,时间充分经过后变为恒定状态时,电流源晶体管112的漏极电流确定为控制电流。这样,在电流源电容111中保持控制电流为漏极电流时的栅极电压。之后,电流保持晶体管804为非导通状态。这样,电流源电容111中保持的电荷也分配到电流停止晶体管805的栅极。如此,电流保持晶体管804为非导通状态的同时,电流停止晶体管805自动为导通状态。

图57(F)所示期间TD4中,电流输入晶体管803为非导通状态。这样,像素中不输入控制电流。电流保持晶体管804为非导通状态的定时相对电流输入晶体管803为非导通状态的定时提前或同时较好。这是由于不使电流源电容111中保持的电荷放电。期间TD4以后施加端子A和端子B之间的电压的情况下,经电流源晶体管112和电流停止晶体管805输出一定电流。即,电流源电路102输出控制电流时,电流源晶体管112和电流停止晶体管805像1个多栅型晶体管一样发生作用。因此,对于输入的控制电流,即基准电流,可将输出的一定电流值设定得小。因此,由于增大基准电流可加速电流源电路的设定动作。这样,需要电流停止晶体管805和电流源晶体管112的极性相同。希望电流停止晶体管805和电流源晶体管112的电流特性相同。这是由于具有多栅方式1的各电流源电路102中,电流停止晶体管805和电流源晶体管112的特性不一致的情况下,输出电流产生偏差。

多栅方式1的电流源电路中,不仅电流停止晶体管805,也可使用输入控制电流的变换为对应的栅极电压的晶体管(电流源晶体管112)输出来自电流源电路102的电流。另一方面,实施形式1所示的电流镜方式的电流源电路中,输入控制电流的变换为对应的栅极电压的晶体管(电流晶体管)和将该栅极电压变换为漏极电流的晶体管(电流源晶体管112)完全不同。因此,与电流镜方式的电流源电路相比,多栅方式1的电流源电路降低晶体管的电流特性偏差对电流源电路102的输出电流的影响。

多栅方式1的电流源电路的各信号线可共用。例如,电流输入晶体管803和电流保持晶体管804按相同定时切换导通状态、非导通状态,则动作上没有问题。因此,电流输入晶体管803和电流保持晶体管804极性相同,可共用信号线GN和信号线GH。

多栅方式1中,电流源电路的部分在像素的设定动作时为图63(a)所示,发光时如图63(b)所示。即这样,可连接布线和开关部。例如可如图68那样连接。

具有上述结构的开关部和电流源电路的像素中,图74表示各布线共用的具体例子。图74(A)~74(D)中信号线GN和信号线GH共用,布线Wco和电源线W共用。尤其图74(A)中,电流保持晶体管804的源极端子或漏极端子中,将不与电流源电容111的一个电极连接的侧直接连接电流线CL。删除晶体管304串联连接电流源晶体管112和驱动晶体管302。图74(B)中,在选择电流源晶体管112的源极端子和电源线W的连接的位置上连接删除晶体管304。图74(C)中,为电源线W顺序经开关部101、电流源电路102连接发光元件106的结构。该结构中,设置追加晶体管390。追加晶体管390连接电源线W和电流源晶体管112的源极端子,使得在开关部关的状态下,即驱动晶体管302为非导通状态下进行像素的设定动作。图74(D)中,电流保持晶体管804连接在电流源晶体管112的栅极和漏极之间。并且删除晶体管304并联连接保持电容303。像素的设定动作时,无论驱动晶体管302处于何种状态,都不向驱动晶体管302流入电流。这是由于电流停止晶体管805的栅极和源极之间的电压为零,自动将电流停止晶体管805设为关状态。

实施形式1所示的电流镜方式的电流源电路中,输入发光元件的信号是按规定倍率增减输入像素的控制电流的电流。因此,可将控制电流设定得大到一定程度,加快进行各像素的电流源电路的设定动作。但是,出现构成电流源电路具有的电流镜面电路的晶体管的电流特性有偏差和图像显示有偏差的问题。另一方面,同一晶体管方式的电流源电路中,输入发光元件的信号与输入像素的控制电流的电流值相等。这里,同一晶体管方式的电流源电路中,输入控制电流的晶体管和向发光元件输出电流的晶体管相同。因此,晶体管的电流特性偏差带来的图像的不均被降低。

与此不同,多栅方式的电流源电路中,输入发光元件的信号是按规定倍率增减输入像素的控制电流的电流。因此,可将控制电流设定得大到一定程度。由此,加快进行各像素的电流源电路的设定动作。输入控制电流的晶体管和向发光元件输出电流的晶体管部分共用,因此与电流镜方式的电流源电路相比,晶体管的电流特性偏差带来的图像的不均被降低。

接着在下面表示多栅方式的电流源电路的情况下的设定动作和开关部的动作的关联。多栅方式的电流源电路的情况下,输入控制电流期间,不能输出一定电流。因此,开关部的动作和电流源电路的设定动作需要同步进行。例如,可仅在开关部关状态的情况下,进行电流源电路的设定动作。即,与同一晶体管方式大致相同。因此,图像显示动作(开关部的驱动动作)和电流源电路的设定动作(像素的设定动作)也与同一晶体管方式大致相同,省略说明。

接着叙述本发明的实施例,该发明不限定于下面实施例。

(实施例1)

本实施例中,是具有电流镜方式的电流源电路的像素结构,举出使用与实施形式1中,图4所示的结构的电流源电路不同的结构的电流源电路的像素结构的例子。

各像素中配置的电流源电路的结构例子在图17表示。图17中与图4相同部分使用相同附图标记,省略说明。图17中,电流源电路102除电流源电容111、电流源晶体管112、电流晶体管1405、电流输入晶体管1403、电流保持晶体管1404、电流线CL、信号线GN、信号线GH外,还具有点顺序晶体管2404和点顺序线CLP。与图4不同的是追加点顺序晶体管2404的部分。点顺序晶体管2404为n沟道型,但由于仅作为开关动作,也可以是p沟道型。

电流源晶体管112的栅极和电流晶体管1405的栅极以及电流源电容111的一个电极连接。电流源电容111的另一电极连接电流源晶体管112的源极端子和电流晶体管1405的源极端子,连接电流源电路102的端子A。电流晶体管1405的栅极顺序经电流保持晶体管1404的源极和漏极端子之间和点顺序晶体管2404的源极和漏极端子之间连接其漏极端子。电流保持晶体管1404的栅极连接信号线GH。点顺序晶体管2404的栅极连接信号线点顺序线CLP。电流晶体管1405的漏极端子和电流线CL经电流输入晶体管1403的源极和漏极端子之间而连接。电流输入晶体管1403的栅极连接信号线GN。电流源晶体管112的漏极端子连接端子B。

上述结构中,电流输入晶体管1403可配置在电流晶体管1405和端子A之间。即,为电流晶体管1405的源极端子经电流输入晶体管1403源极·漏极端子之间而连接端子A,也可以是电流晶体管1405的漏极端子连接电流线Cl的结构。任何一种中,电流源电路部分在像素的设定动作时为图61(a)所示,发光时为图61(b)所示。

上述结构中,电流晶体管1405和电流源晶体管112的栅极可不经电流输入晶体管1403的源极和漏极端子之间而连接电流线CL。即,点顺序晶体管2404的源极端子和漏极端子的不与电流保持晶体管1404的源极端子或漏极端子连接的侧直接连接电流线CL的结构也可。当然不限定于此,电流保持晶体管1404和点顺序晶体管2404连接成二者都为导通状态时,电流晶体管1405的栅极电位与电流线CL的电位相等。

可更换电流保持晶体管1404和点顺序晶体管2404的配置。即,电流晶体管1405的栅极顺序经电流保持晶体管1404的源极和漏极端子之间和点顺序晶体管2404的源极·漏极端子之间连接其漏极端子,电流晶体管1405的栅极顺序经点顺序晶体管2404的源极·漏极端子之间和电流保持晶体管1404的源极·漏极端子之间连接其漏极端子。

图17中对图4追加点顺序晶体管2404,点顺序晶体管2404串联连接电流保持晶体管1404。通过该结构,电流源电容111只要电流保持晶体管1404和点顺序晶体管2404二者不为导通状态就保持电荷。这样,通过追加点顺序晶体管2404,并非按图4的线顺序而是按点顺序进行像素的设定动作。具有图17所示的结构的电流源电路102和图13所示结构的开关部101的像素100按x列y行矩阵状配置的像素区域的一部分电路图在图18表示。

图18中,仅代表性地表示出第i行(i是自然数)第j列(j是自然数)、第(i+1)行第j列、第i行第(j+1)列、第(i+1)行第(j+1)列的4像素。图17和图13相同的部分用相同附图标记表示,省略说明。对应第i行、第(i+1)行的各个像素行的扫描线G表示为Gi,Gi+1、删除用信号线表示为RGi,RGi+1、信号线GN表示为GNi,GNi+1、信号线GH表示为GHi,GHi+1。对应第j列、第(j+1)列的各个像素列的图像信号输入线S表示为Sj,Sj+1、电源线W表示为Wj,Wj+1、电流线CL表示为CLj,CLj+1、布线Wco表示为Wcoj,Wcoj+1、点顺序线CLP表示为CLPj,CLPj+1。从像素区域外部向电流线CLj,CLj+1中输入基准电流。

发光元件106的像素电极连接端子D,对置电极被施加对置电位。图18中,表示出将发光元件的像素电极作为阳极、将对置电极作为阴极的结构。即,表示出电流源电路的端子A连接电源线W,端子B连接开关部101的端子C的结构。但是,在发光元件106的像素电极为阴极、对置电极为阳极的结构的显示装置中,也容易应用本实施例的结构。

为确定电流线CLj,CLj+1流过的基准电流,用404模式地表示出在像素区域外部设置的电流源(下面叫参考电流源电路)。使用来自1个参考电流源电路404的输出电流可向各电流线CL流入基准电流。这样,抑制流过各电流线的电流的偏差,将流过全部电流线的电流正确地确定为基准电流。

由参考电流源电路404确定的基准电流输入各电流线CL1~CLx的电路叫切换电路,图18中用2405表示。切换电路2405的结构例子在图20中表示。切换电路2405具有脉冲输出电路2711、采样脉冲线2710_1~2710_x和开关2701_1~2701_x。

从脉冲输出电路2711输出的脉冲(采样脉冲)输入采样脉冲线2710_1~2710_x。通过输入采样脉冲线2710_1~2710_x的信号,开关2701_1~2701_x顺序为开状态。经开状态的开关2701_1~2701_x,参考电流源电路404连接各电流线CL1~CLx。同时,采样脉冲也输入点顺序线CLP1~CLPx。例如,通过输入第j采样脉冲线2710_j的采样脉冲连接电流线CLj和参考电流源电路404,同时采样脉冲输出到点顺序线CLPj。

这里,点顺序线CLPj上连接点顺序晶体管2404的像素中,点顺序晶体管2404为导通状态时,通过输入某行的信号线GN和GH的信号将连接该信号线GN和GH的电流输入晶体管1403和电流保持晶体管1404设为导通状态。这样,可仅在电流保持晶体管1404和点顺序晶体管2404都为导通状态的像素中将信号输入电流源电容111中。由此。可通过点顺序进行像素的设定动作。

图19是表示图18所示的各像素中配置的电流源电路102的设定动作(像素的设定动作)的定时图。图19中进行第i行像素的设定动作的期间用SETi表示。SETi中,进行第i行的第一列到第x列的像素的设定动作。在此,第i行的第一列到第x列的像素的设定动作在图19中分为SETi的(1)和(2)期间。

在SETi的期间(1)中,通过输入信号线GNi和信号线GHi的信号,图18所示的第i行的像素的电流输入晶体管1403和电流保持晶体管1404为导通状态。之后,一列一列地顺序选择各列的CLP和开关2701。作为一个例子,说明第i行,即第i行第j列的像素的设定动作。这里,在SETi的期间(1)中,进行第i行第j列的像素的设定动作的期间用SET(i,j)表示。SET(i,j)中通过切换电路2405,电流线CLi连接参考电流源电路404。这样基准电流流过电流线CLi。同时通过从切换电路2405输入点顺序线CLPj的信号,点顺序晶体管2404为导通状态。图19的定时图中,CLj表示的期间表示电流线CLi和参考电流源电路404连接的期间。这样,SET(i,j)中,第i行第j列的像素的电流保持晶体管1404、点顺序晶体管2404、电流输入晶体管1403为导通状态。因此,第i行第j列的像素的电流晶体管1405为栅极·源极间电压(栅极电压)与源极·漏极间电压相等的状态,即饱和区域动作,流过漏极电流。经过充分时间变为恒定状态后,在电流源电容111中储存电荷,流过电流晶体管1405的漏极电流确定为流过电流线CLj的基准电流。

之后,SET(i,j)结束后,第i行第j列的像素的点顺序晶体管为非导通状态。这样,第i行第j列的像素的电流源电容111保持电流晶体管1405流过基准电流时的栅极电压。以上动作1列1列地反复进行。

直到SET(i,1)~SET(i,x)结束,第i行的全部像素的电流源电容111中保持对应流过电流线CL的基准电流的电荷。之后进入期间(2)。期间(2)结束后,信号线GNi和信号线GHi的信号变化,第i行的像素的电流输入晶体管1403和电流保持晶体管1404为非导通状态。图18所示的像素结构的显示装置中,可更换电流保持晶体管1404和点顺序晶体管2404的配置。但是图18所示的像素结构的显示装置根据图19所示的定时图驱动的情况下,各像素的点顺序晶体管2404比电流保持晶体管1404更多地进行导通状态、非导通状态的切换。因此,为不对电流源电容111中保持的电荷产生影响,导通状态和非导通状态的切换少的电流保持晶体管1404连接电流源电容111的结构较好。

(实施例2)

本实施例中,是具有同一晶体管方式的电流源电路的像素结构,举出使用与实施形式2中,图12所示的结构的电流源电路不同的结构的电流源电路的像素结构的例子。

开始图21表示出本实施例的电流源电路的结构例子。图21中,与图12相同部分使用相同附图标记表示。本实施例也可实施例1同样通过点顺序进行像素的设定动作。

图21中,电流源电路102除电流源电容111、电流源晶体管112、电流输入晶体管203、电流保持晶体管204、电流停止晶体管205、电流线CL、信号线GN、信号线GH、信号线GS外,还具有点顺序晶体管208和点顺序线CLP。与图12不同的是追加点顺序晶体管208的部分。点顺序晶体管208为n沟道型,但由于仅作为开关动作,可以是p沟道型。

电流源晶体管112的栅极和电流源电容111的一个电极连接。电流源电容111的另一电极连接电流源晶体管112的源极端子。电流源晶体管112的源极端子连接电流源电路102的端子A。

电流源晶体管112的栅极顺序经电流保持晶体管204的源极和漏极端子之间和点顺序晶体管208的源极和漏极端子之间连接其漏极端子。电流保持晶体管204的栅极连接信号线GH。点顺序晶体管208的栅极连接点顺序线CLP。电流源晶体管112的漏极端子和电流线CL经电流输入晶体管203的源极和漏极端子之间而连接。电流输入晶体管203的栅极连接信号线GN。电流源晶体管112的漏极端子经电流停止晶体管205的源极和漏极端子之间连接端子B。电流停止晶体管205的栅极连接信号线GS。

上述结构中,电流源晶体管112的栅极可不经电流输入晶体管203的源极·漏极端子之间而连接电流线CL。即,点顺序晶体管208的源极端子和漏极端子的不与电流保持晶体管204的源极和漏极端子连接的侧直接连接电流线CL的结构也可。当然不限定于此,电流保持晶体管204和点顺序晶体管208连接成二者都为导通状态时,电流源晶体管112的栅极电位与电流线CL的电位相等。

这里可更换电流保持晶体管204和点顺序晶体管208的配置。也可为电流源晶体管112的栅极顺序经电流保持晶体管204的源极和漏极端子之间和点顺序晶体管208的源极和漏极端子之间连接其漏极端子的结构,也可以是电流源晶体管112的栅极顺序经点顺序晶体管208的源极和漏极端子之间和电流保持晶体管204的源极和漏极端子之间连接其漏极端子的结构。

即,图21中对图12追加点顺序晶体管208,点顺序晶体管208串联连接电流保持晶体管204。通过该结构,电流源电容111只要电流保持晶体管204和点顺序晶体管208二者不为导通状态就保持电荷。这样,通过追加点顺序晶体管208,并非按图12的线顺序而是按点顺序进行像素的设定动作。

具有图21所示的结构的电流源电路102和图13所示结构的开关部101的像素100按x列y行矩阵状配置的像素区域的一部分电路图在图22表示。图22中,仅代表性地表示出第i行第j列、第(i+1)行第j列、第i行第(j+1)列、第(i+1)行第(j+1)列的4像素。图21和图13相同的部分用相同附图标记表示,省略说明。