CN1011085B - 用于测试集成电路元件的电路结构 - Google Patents

用于测试集成电路元件的电路结构Info

- Publication number

- CN1011085B CN1011085B CN86105604A CN86105604A CN1011085B CN 1011085 B CN1011085 B CN 1011085B CN 86105604 A CN86105604 A CN 86105604A CN 86105604 A CN86105604 A CN 86105604A CN 1011085 B CN1011085 B CN 1011085B

- Authority

- CN

- China

- Prior art keywords

- circuit

- test

- circuit structure

- testing

- circuit component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318516—Test of programmable logic devices [PLDs]

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/006—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation at wafer scale level, i.e. wafer scale integration [WSI]

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/92—Conductor layers on different levels connected in parallel, e.g. to reduce resistance

Abstract

用于测试电路元件的电路结构,该电路元件作为集成电路形成于一块公共基片上,并可经基片上的公共供电和输入线操作,该电路结构的测试电路和开关单元作为集成电路形成在同一基片上,开关单元可由测试电路控制并插在连接测试电路和电路元件的连线中,测试电路装有传递测试结果的输出电路,在测试电路元件时,测试电路除电源线外没其它连线,自测试是利用测试电路的中央单元比较实际和期望值来判别元件合格与否,并顺时地确定其功能度。

Description

本发明涉及一种用于测试集成电路元件的电路结构。该结构把测试电路和开关单元以集成电路的形式,一起形成在一块公共基片上,并可通过基片上的公共供电线来操作,开关单元由一包括有用于输出测试数据的输出电路的测试电路所控制。

这种类型的电路结构在“电气与电子工程师协会”(IEEE)的会刊1982年1月Volume 70,Nol,第59至78页,由Frank F.Tsui所著的“在现场具有测试能力的结构”一文中已作了描述。在这种已知的电路结构中,在构成多个集成电路元件(芯片)的基片(晶片)上带有许多与单个或所有电路元件连接的外部连接区(基座)。通过适当的接口,测试设备被连接到这些外部引线上。借助于这种测试设备,来测试基片上的电路元件。但是,对这种结构来说,假定其中的电路元件是数字单元,除了为正常工作需要的结构元件外,附加的结构元件是与控制线结合在一起的。利用这样的结构,测试时的电路元件能被转换成为操作状态,在这种状态下,所有的结构元件的功能度均能被测定。由于附加了这种结构元件,电路元件的某些有用的表面部分被浪费掉了,所需要的附加连线又使实际工作中有用的连线数目减少了。由于把基片连接到测试电路的接口,在整个测试过程中,接口一直是被占用的,因此,除非减少测试时间,以测试结果不准确和不完全为代价,否则被测试基片的通过速度是低的。

在过去的其它刊物上已提出过在每个电路元件内部永久性地设置其本身的测试电路。这就会浪费掉大部分电路元件面积和最后完成的单元

的可用外部连线。而且,要对这些电路元件单独地进行测试是非常费时的。电路元件的误差仅在边界条件(final condition)下进行检测,以致许多制造步骤均需要达到边界条件,结果浪费了时间。

本发明的目的是开发一种能经济地测试集成电路元件的电路结构。

该目的是通过本发明的具有如下特征的电路结构来实现的,让测试电路(3)把测试中获得的实际值与至少一个要测试的参数的期望值进行比较,该测试电路包括一个中央单元(4),用来测试多个电路元件(2),并就至少一个测试参数而言,用来判断电路元件的失效和不失效,以及用来按时间顺序地判定电路元件的各自的功能度。

在本发明中,与先有技术相比和被测电路需要的面积有关的测试电路所需面积是明显地减少了,由于减少了为测试所生产的集成电路所耗用的更多附加面积的成本,因而生产这种自测试集成电路是经济的。

相应地,在根据本发明的电路结构中,在电路元件的基片上形成有专门用于测试的电路。为了执行各个测试步骤,测试电路通过基片上的各个被控制的开关单元和连接线与各个电路元件相连。测试的结果通过测试电路的输出电路传送。因此,基片仅仅被连接到为测试用的一个合适的电源上,基片上的电路元件在测试之后能自动地导通。所以,这种方便的连接,有可能采用合理的方法,同时地对多个基片或基片上的各个电路元件进行测试。电路元件可以是模拟和/或数字电路,而且,不需要为了测试而包含专用部件。再者,在同一块基片上可以形成不同类型的电路元件。因此,并不限于个别的电路类型。在各个基片上形成的测试电路,只要根据所需要的测试过程及其精度来设计。这表明与一般的测试装置相比,这样的结构是大大地简化了,对传统结构来说,还必须考虑不同电路类型和不同测试要求的各种应用场合。测试电路和开关单元在基片上要占一定的面积,但是这一面积与电路元件所占的面积比较起来是相当小的。并不需要为了测试目的对电路元件本身作什么变

动,因此,在这里并没有浪费掉有用的面积,而且也保持了实际工作的可用连线的数目。当测量单独的电路元件非常费时时,诸如在大容量存贮器,信息处理机场合或类似的情况下,利用基于本发明的电路结构,能对多个基片上的电路元件简单地同时测试而尤其有利。

根据本发明的电路结构的最佳实施例将在后面加以说明。

现在将参照附图中的例子对本发明作详细介绍,附图中:

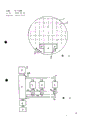

图1是根据本发明电路结构的一个实施例的平面视图;

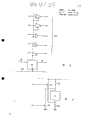

图2是该电路结构的简图;

图3表示用于该电路结构中的一个开关单元的一个例子;

图4表示对被测电路元件供电的一个例子。

图1是基片1的一个概略的平面视图,在基片1上,多个被测电路元件2形成集成电路。为了进行测试,在基片1的由粗线围绕的部分形成有测试电路3,在本实施例中,测试电路包括中央单元4,程序存贮器5,和一个带有结果存贮器6和显示器件7的输出电路,此外,基片1上还具有用来为外部连接用的连接区8。

基片1是(例如)一般用于半导体生产中的半导体片(晶片)。根据要在其上形成的电路元件的特性,基片1也可以是任何其它衬底,和具有其它形状,例如是矩形的。被测试的电路元件2可以是数字的,模拟的或数/模混合电路。根据所要求的作用原理,电路元件2可以全部或部分地包含超导体,有机物或生物开关元件,光波导体和相类似的材料。它们可被设计成具有各种功能,就是说,它们可以是从简单的开关元件或放大器一直到大容量存贮器构成的组件。如果电路元件2是用作非易失型存贮器,则它们首先被做成可编程存贮器的形式,然后,在测试过程中,或测试应把期望的固定值编入到程序中。如果电路元件为带有附加电池的存贮器形式,对于后者,如果必要,当测试发现“坏了”时,则可以用开关转换,以便代替这些电池。

测试电路3在基片1上占有比单独的电路元件2更大的面积,但是这样一来免去了安装在每个电路元件内的分立的测试电路,如果把每个电路元件中的测试电路合在一起,则甚至要占用更大的面积,特别会使电路元件中的功能件的数目减少。

测试电路3包含有一种带有中央单元4和程序存贮器5的微处理器。中央单元4包括:用于连接到开关单元2和用于控制这些连线的接口;用于产生测试信号,时钟信号,控制信号以及类似信号的振荡器;用于控制程序执行等的时间发生器。中央单元4也可包含自测电路和带有备用单元或备用通道,如果通过自测表明中央单元或通道已失效时,则可以用连接备用单元或通道来代替。中央单元4执行贮存在程序存贮器中5的测试程序。测试程序将根据待测电路元件的特性,被测参数的种类,要求的精度以及类似的要求来设计。因此,可以为程序存贮器5准备适当的程序模式,并有选择地使用与中央单元4的电路模式保持一致的程序。

此外,测试电路3包含具有结果存贮器6和显示器件7的输出电路。和程序存贮器5的情况一样,结果存贮器6能根据待测电路元件和测试规范来设计,而且和程序存贮器一样,也能有选择地应用。结果存贮器6可以贮存“好/坏”数据,误差类型的数据,质量范围的数据以及类似的数据,这些数据是作为测试结果通过中央单元4引入的。测试数据被贮存在结果存贮器6的予定的存贮位置中,这些位置是与各个电路元件2有关的。结果存贮器6最好是诸如可编程序只读存贮器之类的非易失存贮器形式,在这类存贮器中,贮存的内容可由中央单元4检索,例如,为了打印测试结果或进行修理或根据测试结果打标记,如果有可能去修复基片1上的不合格电路元件2(例如,利用激光束),则结果存贮器6将采用可擦可编程序存贮器(EPROM)的形式,该存贮器在电路元件2完全修复后,可擦去原来的测试结果,并用来贮存新的测试

结果。显示器7用来把所需范围的测试结果给出一个可见的显示。显示器件7可根据结果存贮器(6)的内容进行工作或其本身包含用于某些测试结果(如关于质量等级)的存贮单元。显示器件7对每个待测电路元件2包含至少一个显示元件,例如发光二级管或易熔连线是最理想的,该连线熔断时能用光学方法检测。根据图1,显示器件7的显示元件被组合在一个显示区域中,在该区域中,显示元件是以与电路元件2相同的图样排列的。测试结束后,为了进行误差分析,可对该显示区域自动地加以评价和/或用放大镜或显微镜来检查,并用墨水对不合格的电路元件打上标记,当误差的数量超过一定值时,就报废整个基片以及其它等等。虽然在图中没有说明,也可把显示区域或附加在其内的显示元件安排在对应的电路元件2的附近。当在评价测试结果时,这种安排能简化地址分配。

基片1上的连线区域8用于为电路元件2和测试电路3供电,还用于数据的输入和输出,例如,通过相应的连线区域8,可以输出结果存贮器6的内容,以用来记录或类似的目的,或为开始测试,或对某一特定部分测试,或根据某些测试结果,执行附加的测试而对中央单元4输入一个指令。

按照图2所示的方法,测试电路3经由连线和开关单元被连到电路元件2。根据图2,输入总线9引到各个电路元件2的输入端而电路元件的输出端经过各自的开关单元10,在测试电路3的控制下连到公共输出总线11,输出总线11又引回到测试电路3中的中央单元4。开关单元10通过控制线12和13由中央单元4控制。在图2所示的情况下,开关单元10以移位寄存器的形式连接成链式电路,在这个链式电路中,开关单元经过被环绕或步进线形式的控制线12依次导通和断开,控制线13在这里用来为步进发送时钟信号。

为了测试单个电路元件2,相应的开关单元10导通,而所有其它的

开关单元被关闭。电路元件2通过输入总线9接收一定的输入信号,这些信号把适当的输出信号引到输出总线11上。测试电路3借助中央单元4检测实际出现于输出总线11上的信号是否与期望的信号相符或是否在期望的范围之内。

同样的开关单元10也可以连接在总线9和电路元件2的输入端之间,并分别同电路元件输出端的相应的开关单元10一起受到控制。因而,能防止中央单元4的输出级因驱动接到许多电路元件2输入端的总线9而过载。

图3示出了一个开关单元10的结构的实施例。开关单元10包括一个贮存元件14和至少一个开关元件15。贮存元件14是触发器型的,该触发器在图3的整个电路中是链式电路的一部分,该开关根据前面开关单元10的开关状态,在控制线13上的时钟信号控制下经由步进线12来转换。贮存元件14的输出信号用来转换被连接的开关元件15,在图3中示出了开关元件的几个例子。根据图3,一个特定的开关元件15可以是开关型缓冲器或放大器,开关型反相器,与门,与非门或开关晶体管。根据电路元件2的特性,开关元件可以是模拟或数字开关元件型的。此外,开关单元10可以包含多个如图3的单元,这些单元用于为依次的测试步骤,诸如信号变换,电平转换,信号组合以及其它类似的步骤给出不同的测试状态。

图4示出了为各个电路元件2供电的图。在图4的例子中,每个电路元件2的两根电源线均包含有保险丝16,该保险丝在电流过大时熔断,这种熔断状态最好可用光学方法来确认。熔丝16作为保险丝用来切断有故障电路元件2,这种有故障电路元件将妨碍对所有电路元件供电,从而使测试不能进行。另外,图4示出了两个开关晶体管17,利用该晶体管,在测试电路3的控制下,为了对已发现的不合格电路元件做上标记,或为了避免(例如)通过“杂散振荡”(wild oscillations)使测试

受到影响,可以加上一个电压有意地使特定的保险丝16熔断。这种保险丝16也可以加在各个电路元件2的特定的输入和输出线上,以致任何短路将不会使中央单元4受到影响。另外,为了减少测试期间的功率消耗,可以用其它的开关晶体管(未示出)来代替保险丝16或在其上附加一个晶体管,该晶体管在测试电路3的控制下,仅仅能使一个电路元件2或其中的一组被加上电流。

开关单元10,输入输出总线9,11以及保险丝16和开关晶体管17与电源线一起,被安排在基片1的所要求的部位,当基片1用激光束或其它方法割成单个电路元件时,该部位就被省去了。基片1被分割后,即获得一个已被测试过的,并仅仅包含结构元件和为实现其功能所必要的连线的电路元件2。

图1仅仅示出了测试电路3和电路元件2合在一起的结构的一个例子。另一方面,测试电路3也能沿基片1的周缘排列而不象图1那样排列在一侧,也能排列在基片1的中间可使引线更短,当用不同的电路元件2装备基片1时,可以配备不同的可检索程序存贮器。

根据上述实施例,对带有导线和开关单元的用电信号来测试电路元件的电路结构已经作了说明。但是,同样地用来测试电路元件的电路结构也能这样构成,在这种结构中,至少部分地使用光导体,超导体,有机物导体或类似的材料。在那种情况下,电路结构的各个连线和开关元件必需被适当地构成。

图1中所示的测试电路3处在电路元件2以外的区域,但是测试电路的某些部分,例如,测试信号放大器,数字缓冲器,范围极限开关等等也能安排在线路元件的输出或输入端附近,以消除由过长的测试信号线所引起的误差影响。

Claims (16)

1、用于测试集成电路元件的电路结构,该结构把测试电路和开关单元以集成电路的形式,一起形成在一块公共基片上,并可通过基片上的公共供电线来操作,开关单元由测试电路控制,该测试电路包括用于输出测试数据的输出电路,特征在于:测试电路(3)被安排成用于把测量中获得的实际值与至少一个要测试的参数的期望值相比较,测试电路包括一个中央单元(4),和程序存贮器(5),所述中央单元被配置成用来测试多个电路元件(2),并就至少一个测试参数而言,用来判断电路元件的合格和不合格,以及按时间顺序地判定电路元件的各自的功能度;所述输出电路包括,结果存贮器(6)和显示器件(7)。

2、根据权利要求1的电路结构,特征在于测试电路(3)中的中央单元(4)包括微处理器。

3、根据权利要求1或2的电路结构,特征在于测试电路(3)被设计成自测试型的,并包含能根据自测试结果被转换接通的等同电路组。

4、根据权利要求1或2的电路结构,特征在于每个电路元件(2)的电源能由测试电路(3)接通和关断。

5、根据权利要求1或2的电路结构,特征在于各个电路元件(2)经过熔丝(16)连接到电源线,该熔丝在相关的电路元件内部短路时熔断,或可通过由测试电路(3)操作的晶体管(17)加上电源电压而熔断。

6、根据权利要求1或2的电路结构,特征在于所述结果存贮器(6)的存贮位置分配给各个电路元件(2),用来贮存有关电路元件的功能度方面的信息。

7、根据权利要求6的电路结构,特征在于所述结果存贮器(6)是非易失型存贮器。

8、根据权利要求1或2的电路结构,特征在于所述结果存贮器(6)能通过基片(1)的外部连线(8)读出。

9、根据权利要求1或2的电路结构,特征在于所述显示器件(7)可见地显示测试结果的显示器件(7)。

10、根据权利要求9的电路结构,特征在于所述显示器件(7)包括用于每个电路元件(2)的至少一个显示元件,所述显示元件被安置于每个有关电路元件(2)的附近或单独的显示区域内。

11、根据权利要求10的电路结构,特征在于所述显示元件是发光二极管或易熔连线,该熔丝的熔断状态能用肉眼辨别。

12、根据权利要求11的电路结构,其特征在于所述显示器件(7)根据结果存贮器(6)的内容进行工作或其本身包含用于某些测试结果的存贮单元。

13、根据权利要求1或2的电路结构,特征在于所述开关单元(10)和/或连接所述开关单元与测试电路的连线(9,11)被形成于基片(1)的一个区域中,当基片被切割后,该区域就完全脱离了。

14、根据权利要求1或2的电路结构,特征在于每个所述开关单元(10)包括一个存贮器元件(14)和至少一个被控的开关元件(15),从而把连线(9,11)中的一根转接到相应的电路元件(2)上。

15、根据权利要求14的电路结构,特征在于所述存贮器元件(14)被连成一个链式电路,该链式电路中存贮器的接通状态能被移位。

16、根据权利要求1或2的电路结构,特征在于由所述测试电路(3)的测试结果所断定不合格的电路元件(2)的至少一根公共电源线和/或连线(9,11)能被来自测试电路的控制信号暂时或永久地关断。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE19853526485 DE3526485A1 (de) | 1985-07-24 | 1985-07-24 | Schaltungsanordnung zum pruefen integrierter schaltungseinheiten |

| DEP3526485.3 | 1985-07-24 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN86105604A CN86105604A (zh) | 1987-02-11 |

| CN1011085B true CN1011085B (zh) | 1991-01-02 |

Family

ID=6276647

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN86105604A Expired CN1011085B (zh) | 1985-07-24 | 1986-07-24 | 用于测试集成电路元件的电路结构 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US4961053A (zh) |

| EP (1) | EP0212208B1 (zh) |

| JP (1) | JPS6316633A (zh) |

| CN (1) | CN1011085B (zh) |

| AT (1) | ATE67861T1 (zh) |

| DE (2) | DE3526485A1 (zh) |

| IN (1) | IN164539B (zh) |

Families Citing this family (125)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3732830A1 (de) * | 1987-09-29 | 1989-04-06 | Siemens Ag | Schaltungsanordnung zur pruefung der funktionsfaehigkeit einer komplexen schaltung |

| IT1220189B (it) * | 1987-12-22 | 1990-06-06 | Sgs Thomson Microelectronics | Metodo per aumentare incrementalmente in fase di collaudo elettrico su fetta di un dispositivo integrato l'area di collettore di un transistore pnp laterale |

| US6288561B1 (en) * | 1988-05-16 | 2001-09-11 | Elm Technology Corporation | Method and apparatus for probing, testing, burn-in, repairing and programming of integrated circuits in a closed environment using a single apparatus |

| US5206582A (en) * | 1988-05-18 | 1993-04-27 | Hewlett-Packard Company | Control system for automated parametric test equipment |

| US6304987B1 (en) | 1995-06-07 | 2001-10-16 | Texas Instruments Incorporated | Integrated test circuit |

| GB8827629D0 (en) * | 1988-11-25 | 1988-12-29 | Lsi Logic Europ | Testing of analogue circuits |

| US5142224A (en) * | 1988-12-13 | 1992-08-25 | Comsat | Non-destructive semiconductor wafer probing system using laser pulses to generate and detect millimeter wave signals |

| US4956602A (en) * | 1989-02-14 | 1990-09-11 | Amber Engineering, Inc. | Wafer scale testing of redundant integrated circuit dies |

| US5053700A (en) * | 1989-02-14 | 1991-10-01 | Amber Engineering, Inc. | Method for wafer scale testing of redundant integrated circuit dies |

| JPH02129985U (zh) * | 1989-04-04 | 1990-10-26 | ||

| JPH07113898B2 (ja) * | 1989-05-09 | 1995-12-06 | 株式会社日立製作所 | 障害検出方式 |

| US5377124A (en) * | 1989-09-20 | 1994-12-27 | Aptix Corporation | Field programmable printed circuit board |

| US5001604A (en) * | 1989-10-26 | 1991-03-19 | Lusby W Randolph | Embedded testing circuit and method for fabricating same |

| KR920007535B1 (ko) * | 1990-05-23 | 1992-09-05 | 삼성전자 주식회사 | 식별회로를 구비한 반도체 집적회로 칩 |

| US5059899A (en) * | 1990-08-16 | 1991-10-22 | Micron Technology, Inc. | Semiconductor dies and wafers and methods for making |

| US7511520B2 (en) * | 1990-08-29 | 2009-03-31 | Micron Technology, Inc. | Universal wafer carrier for wafer level die burn-in |

| US5905382A (en) * | 1990-08-29 | 1999-05-18 | Micron Technology, Inc. | Universal wafer carrier for wafer level die burn-in |

| EP0481703B1 (en) * | 1990-10-15 | 2003-09-17 | Aptix Corporation | Interconnect substrate having integrated circuit for programmable interconnection and sample testing |

| JPH04218939A (ja) * | 1990-12-19 | 1992-08-10 | Sharp Corp | 集積回路装置 |

| DE69219165T2 (de) * | 1991-01-11 | 1997-08-07 | Texas Instruments Inc | Prüf- und Einbrennsystem für einen Wafer und Methode für deren Herstellung |

| JP2936807B2 (ja) * | 1991-07-12 | 1999-08-23 | 日本電気株式会社 | 集積回路 |

| US5206583A (en) * | 1991-08-20 | 1993-04-27 | International Business Machines Corporation | Latch assisted fuse testing for customized integrated circuits |

| US5315241A (en) * | 1991-09-18 | 1994-05-24 | Sgs-Thomson Microelectronics, Inc. | Method for testing integrated circuits |

| US5262719A (en) * | 1991-09-19 | 1993-11-16 | International Business Machines Corporation | Test structure for multi-layer, thin-film modules |

| JPH0590362A (ja) * | 1991-09-26 | 1993-04-09 | Hitoshi Nishimura | 半導体ウエハの検査構造 |

| US5198760A (en) * | 1991-09-30 | 1993-03-30 | Hughes Aircraft Company | Method by which to detect direction of current flow in outputs of integrated circuits |

| US5311122A (en) * | 1991-12-02 | 1994-05-10 | Motorola, Inc. | RF test equipment and wire bond interface circuit |

| JPH05198637A (ja) * | 1992-01-23 | 1993-08-06 | Mitsubishi Electric Corp | 半導体集積回路及びそのテスト方法 |

| US5279975A (en) * | 1992-02-07 | 1994-01-18 | Micron Technology, Inc. | Method of testing individual dies on semiconductor wafers prior to singulation |

| JPH05267415A (ja) * | 1992-03-18 | 1993-10-15 | Fujitsu Ltd | 半導体装置 |

| US5241266A (en) * | 1992-04-10 | 1993-08-31 | Micron Technology, Inc. | Built-in test circuit connection for wafer level burnin and testing of individual dies |

| US5457400A (en) * | 1992-04-10 | 1995-10-10 | Micron Technology, Inc. | Semiconductor array having built-in test circuit for wafer level testing |

| US5332973A (en) * | 1992-05-01 | 1994-07-26 | The University Of Manitoba | Built-in fault testing of integrated circuits |

| US5648661A (en) * | 1992-07-02 | 1997-07-15 | Lsi Logic Corporation | Integrated circuit wafer comprising unsingulated dies, and decoder arrangement for individually testing the dies |

| US5442282A (en) * | 1992-07-02 | 1995-08-15 | Lsi Logic Corporation | Testing and exercising individual, unsingulated dies on a wafer |

| US5389556A (en) * | 1992-07-02 | 1995-02-14 | Lsi Logic Corporation | Individually powering-up unsingulated dies on a wafer |

| JPH06230086A (ja) * | 1992-09-22 | 1994-08-19 | Nec Corp | Lsiのテスト回路 |

| US5286656A (en) * | 1992-11-02 | 1994-02-15 | National Semiconductor Corporation | Individualized prepackage AC performance testing of IC dies on a wafer using DC parametric test patterns |

| FR2700063B1 (fr) * | 1992-12-31 | 1995-02-10 | Sgs Thomson Microelectronics | Procédé de test de puces de circuit intégré et dispositif intégré correspondant. |

| DE4305526A1 (de) * | 1993-02-24 | 1994-08-25 | Telefunken Microelectron | Verfahren zum Betrieb einer integrierten Schaltung |

| US5418452A (en) * | 1993-03-25 | 1995-05-23 | Fujitsu Limited | Apparatus for testing integrated circuits using time division multiplexing |

| US5594273A (en) * | 1993-07-23 | 1997-01-14 | Motorola Inc. | Apparatus for performing wafer-level testing of integrated circuits where test pads lie within integrated circuit die but overly no active circuitry for improved yield |

| US5399505A (en) * | 1993-07-23 | 1995-03-21 | Motorola, Inc. | Method and apparatus for performing wafer level testing of integrated circuit dice |

| US5654588A (en) * | 1993-07-23 | 1997-08-05 | Motorola Inc. | Apparatus for performing wafer-level testing of integrated circuits where the wafer uses a segmented conductive top-layer bus structure |

| FI100136B (fi) * | 1993-10-01 | 1997-09-30 | Nokia Telecommunications Oy | Menetelmä integroidun piirin testaamiseksi sekä integroitu piiri |

| US5418470A (en) * | 1993-10-22 | 1995-05-23 | Tektronix, Inc. | Analog multi-channel probe system |

| US5831918A (en) | 1994-02-14 | 1998-11-03 | Micron Technology, Inc. | Circuit and method for varying a period of an internal control signal during a test mode |

| US6587978B1 (en) | 1994-02-14 | 2003-07-01 | Micron Technology, Inc. | Circuit and method for varying a pulse width of an internal control signal during a test mode |

| US5532174A (en) * | 1994-04-22 | 1996-07-02 | Lsi Logic Corporation | Wafer level integrated circuit testing with a sacrificial metal layer |

| US6055661A (en) * | 1994-06-13 | 2000-04-25 | Luk; Fong | System configuration and methods for on-the-fly testing of integrated circuits |

| US6577148B1 (en) * | 1994-08-31 | 2003-06-10 | Motorola, Inc. | Apparatus, method, and wafer used for testing integrated circuits formed on a product wafer |

| US5508631A (en) * | 1994-10-27 | 1996-04-16 | Mitel Corporation | Semiconductor test chip with on wafer switching matrix |

| JP2725615B2 (ja) * | 1994-10-31 | 1998-03-11 | 日本電気株式会社 | 集積回路試験装置 |

| US5515302A (en) * | 1994-11-07 | 1996-05-07 | Motorola, Inc. | Method for identifying excessive power consumption sites within a circuit |

| US5648730A (en) * | 1994-11-30 | 1997-07-15 | Texas Instruments Incorporated | Large integrated circuit with modular probe structures |

| JP3301874B2 (ja) * | 1994-12-19 | 2002-07-15 | 松下電器産業株式会社 | 半導体装置及びその検査方法 |

| JP3615256B2 (ja) * | 1995-02-10 | 2005-02-02 | 本田技研工業株式会社 | 半導体集積回路 |

| US5617036A (en) * | 1995-02-24 | 1997-04-01 | The Whitaker Corporation | Laser/pin assembly with integrated burn-in assembly |

| US5798653A (en) * | 1995-04-20 | 1998-08-25 | Sun Microsystems, Inc. | Burn-in system for reliable integrated circuit manufacturing |

| EP0745859B1 (en) * | 1995-05-31 | 2004-10-27 | STMicroelectronics, Inc. | Configurable probe pads to facilitate parallel testing of integrated circuit devices |

| US5952838A (en) * | 1995-06-21 | 1999-09-14 | Sony Corporation | Reconfigurable array of test structures and method for testing an array of test structures |

| JP3026308B2 (ja) * | 1995-09-14 | 2000-03-27 | ローム株式会社 | 不揮発性記憶装置および不揮発性記憶装置の製造方法 |

| US6166557A (en) * | 1996-10-31 | 2000-12-26 | Texas Instruments Incorporated | Process of selecting dies for testing on a wafer |

| US5969538A (en) | 1996-10-31 | 1999-10-19 | Texas Instruments Incorporated | Semiconductor wafer with interconnect between dies for testing and a process of testing |

| US5892249A (en) * | 1996-02-23 | 1999-04-06 | National Semiconductor Corporation | Integrated circuit having reprogramming cell |

| US5692084A (en) * | 1996-06-11 | 1997-11-25 | The Whitaker Corporation | Package for an optoelectronic device |

| US5764836A (en) * | 1996-06-11 | 1998-06-09 | The Whitaker Corporation | Pigtailed package for an optoelectronic device |

| US5991214A (en) * | 1996-06-14 | 1999-11-23 | Micron Technology, Inc. | Circuit and method for varying a period of an internal control signal during a test mode |

| US6239604B1 (en) * | 1996-10-04 | 2001-05-29 | U.S. Philips Corporation | Method for inspecting an integrated circuit by measuring a voltage drop in a supply line of sub-circuit thereof |

| US5929650A (en) * | 1997-02-04 | 1999-07-27 | Motorola, Inc. | Method and apparatus for performing operative testing on an integrated circuit |

| US6104198A (en) * | 1997-05-20 | 2000-08-15 | Zen Licensing Group Llp | Testing the integrity of an electrical connection to a device using an onboard controllable signal source |

| DE19742946C2 (de) * | 1997-09-29 | 2000-10-12 | Siemens Ag | Testschaltung auf einem Halbleiter-Chip |

| US6405335B1 (en) | 1998-02-25 | 2002-06-11 | Texas Instruments Incorporated | Position independent testing of circuits |

| DE19819570C2 (de) * | 1998-04-30 | 2000-06-15 | Siemens Ag | Anordnung zum Testen mehrerer Speicherchips auf einem Wafer |

| US6040622A (en) | 1998-06-11 | 2000-03-21 | Sandisk Corporation | Semiconductor package using terminals formed on a conductive layer of a circuit board |

| US6233184B1 (en) * | 1998-11-13 | 2001-05-15 | International Business Machines Corporation | Structures for wafer level test and burn-in |

| US6140833A (en) * | 1998-11-16 | 2000-10-31 | Siemens Aktiengesellschaft | In-situ measurement method and apparatus for semiconductor processing |

| JP4234244B2 (ja) * | 1998-12-28 | 2009-03-04 | 富士通マイクロエレクトロニクス株式会社 | ウエハーレベルパッケージ及びウエハーレベルパッケージを用いた半導体装置の製造方法 |

| DE19917586C2 (de) * | 1999-04-19 | 2002-01-17 | Infineon Technologies Ag | Anordnung zur Durchführung von Burn-In-Behandlungen von Halbleitervorrichtungen auf Waferebene |

| DE19930169B4 (de) * | 1999-06-30 | 2004-09-30 | Infineon Technologies Ag | Testeinrichtung und Verfahren zum Prüfen eines Speichers |

| JP3483130B2 (ja) * | 1999-11-29 | 2004-01-06 | 松下電器産業株式会社 | 集積回路の検査方法 |

| US6214630B1 (en) * | 1999-12-22 | 2001-04-10 | United Microelectronics Corp. | Wafer level integrated circuit structure and method of manufacturing the same |

| US6728915B2 (en) | 2000-01-10 | 2004-04-27 | Texas Instruments Incorporated | IC with shared scan cells selectively connected in scan path |

| US6429677B1 (en) * | 2000-02-10 | 2002-08-06 | International Business Machines Corporation | Method and apparatus for characterization of gate dielectrics |

| DE10010285A1 (de) * | 2000-02-25 | 2001-09-13 | Infineon Technologies Ag | Teststruktur bei integriertem Halbleiter |

| US6769080B2 (en) | 2000-03-09 | 2004-07-27 | Texas Instruments Incorporated | Scan circuit low power adapter with counter |

| WO2001067507A1 (de) * | 2000-03-10 | 2001-09-13 | Infineon Technologies Ag | Test-schaltungsanordnung und verfahren zum testen einer vielzahl von elektrischen komponenten |

| US20020025100A1 (en) * | 2000-06-16 | 2002-02-28 | Mcgill University | Method and apparatus for OPTO-electronic built-in tests |

| DE10037794A1 (de) * | 2000-08-03 | 2002-02-21 | Infineon Technologies Ag | Verfahren und Vorrichtung zum Testen einer integrierten Schaltung, zu testende integrierte Schaltung, und Wafer mit einer Vielzahl von zu testenden integrierten Schaltungen |

| US6462575B1 (en) * | 2000-08-28 | 2002-10-08 | Micron Technology, Inc. | Method and system for wafer level testing and burning-in semiconductor components |

| US6683467B1 (en) * | 2000-09-29 | 2004-01-27 | Intel Corporation | Method and apparatus for providing rotational burn-in stress testing |

| GB0030346D0 (en) * | 2000-12-13 | 2001-01-24 | Mitel Semiconductor Ltd | Integrated circuit test structure |

| US6850075B1 (en) * | 2000-12-22 | 2005-02-01 | Cypress Semiconductor Corp. | SRAM self-timed write stress test mode |

| US6777969B1 (en) * | 2001-03-21 | 2004-08-17 | Cypress Semiconductor Corp. | Low stress test mode |

| TW490783B (en) * | 2001-05-22 | 2002-06-11 | Hi Max Optoelectronics Corp | Testing device and method built in the wafer scribe line |

| JP2003107135A (ja) * | 2001-09-28 | 2003-04-09 | Mitsubishi Electric Corp | バーンイン装置 |

| US6717430B2 (en) * | 2002-02-13 | 2004-04-06 | Motorola, Inc. | Integrated circuit testing with a visual indicator |

| US6825683B1 (en) * | 2002-04-18 | 2004-11-30 | Cypress Semiconductor Corporation | System and method for testing multiple integrated circuits that are in the same package |

| US7026646B2 (en) * | 2002-06-20 | 2006-04-11 | Micron Technology, Inc. | Isolation circuit |

| KR100496862B1 (ko) * | 2002-10-01 | 2005-06-22 | 삼성전자주식회사 | 멀티칩패키지의 테스트 장치 및 방법 |

| DE10258511A1 (de) * | 2002-12-14 | 2004-07-08 | Infineon Technologies Ag | Integrierte Schaltung sowie zugehörige gehäuste integrierte Schaltung |

| KR100523139B1 (ko) * | 2003-06-23 | 2005-10-20 | 주식회사 하이닉스반도체 | 웨이퍼 테스트시 사용되는 프로빙 패드의 수를 감소시키기위한 반도체 장치 및 그의 테스팅 방법 |

| US20050149789A1 (en) * | 2003-11-19 | 2005-07-07 | Honeywell International, Inc. | Pseudo random verification of waveform fault coverage |

| US7365556B2 (en) * | 2004-09-02 | 2008-04-29 | Texas Instruments Incorporated | Semiconductor device testing |

| US7475318B2 (en) * | 2005-01-28 | 2009-01-06 | Honeywell International Inc. | Method for testing the sensitive input range of Byzantine filters |

| JP2007010606A (ja) * | 2005-07-04 | 2007-01-18 | Matsushita Electric Ind Co Ltd | Lsi検査モジュール、lsi検査モジュールの制御方法、lsi検査モジュールとlsi検査装置との通信方法、およびlsi検査方法 |

| US7405585B2 (en) * | 2006-02-14 | 2008-07-29 | Taiwan Semiconductor Manufacturing Co., Ltd. | Versatile semiconductor test structure array |

| US7906982B1 (en) | 2006-02-28 | 2011-03-15 | Cypress Semiconductor Corporation | Interface apparatus and methods of testing integrated circuits using the same |

| JP2007278767A (ja) * | 2006-04-04 | 2007-10-25 | Denso Corp | Ic実装済み電子部品実装基板及びそのリーク電流試験方法 |

| JP2007287770A (ja) * | 2006-04-13 | 2007-11-01 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP4328791B2 (ja) * | 2006-09-20 | 2009-09-09 | エルピーダメモリ株式会社 | 被測定素子の特性測定方法及び半導体装置の特性管理システム |

| JP4274576B2 (ja) * | 2007-01-12 | 2009-06-10 | エルピーダメモリ株式会社 | 半導体装置 |

| WO2008152557A1 (en) * | 2007-06-12 | 2008-12-18 | Nxp B.V. | Semiconductor device test method |

| JP5170395B2 (ja) * | 2008-02-21 | 2013-03-27 | 日本電気株式会社 | ウエハ及びその温度試験方法 |

| US7719299B2 (en) * | 2008-04-02 | 2010-05-18 | Texas Instruments Incorporated | Process and temperature insensitive flicker noise monitor circuit |

| WO2009144791A1 (ja) * | 2008-05-28 | 2009-12-03 | 株式会社アドバンテスト | 試験システムおよび書込用ウエハ |

| US8179143B2 (en) * | 2008-10-15 | 2012-05-15 | Test Research, Inc. | Apparatus for testing printed circuit and method therefor |

| US9759772B2 (en) | 2011-10-28 | 2017-09-12 | Teradyne, Inc. | Programmable test instrument |

| US10776233B2 (en) | 2011-10-28 | 2020-09-15 | Teradyne, Inc. | Programmable test instrument |

| CN103490374B (zh) * | 2013-09-25 | 2017-05-17 | 山东贞明光电科技有限公司 | 一种量产测试设备及其短路过流保护电路 |

| CN103887202B (zh) * | 2014-03-24 | 2016-08-17 | 上海华力微电子有限公司 | 监测方法 |

| US9947712B2 (en) * | 2016-01-27 | 2018-04-17 | Varex Imaging Corporation | Matrix type integrated circuit with fault isolation capability |

| CN109406922B (zh) * | 2017-08-15 | 2020-09-22 | 昆山维信诺科技有限公司 | 电子产品及其测试方法和装置 |

| KR102471500B1 (ko) * | 2018-03-12 | 2022-11-28 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이를 포함하는 테스트 시스템 |

| CN110021334B (zh) * | 2019-04-19 | 2021-08-27 | 上海华虹宏力半导体制造有限公司 | 一种晶圆测试方法 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2330014A1 (fr) * | 1973-05-11 | 1977-05-27 | Ibm France | Procede de test de bloc de circuits logiques integres et blocs en faisant application |

| US4038648A (en) * | 1974-06-03 | 1977-07-26 | Chesley Gilman D | Self-configurable circuit structure for achieving wafer scale integration |

| US4244048A (en) * | 1978-12-29 | 1981-01-06 | International Business Machines Corporation | Chip and wafer configuration and testing method for large-scale-integrated circuits |

| US4243937A (en) * | 1979-04-06 | 1981-01-06 | General Instrument Corporation | Microelectronic device and method for testing same |

| DE3176315D1 (en) * | 1980-04-11 | 1987-08-20 | Siemens Ag | Device for testing a digital circuit with test circuits enclosed in this circuit |

| US4357703A (en) * | 1980-10-09 | 1982-11-02 | Control Data Corporation | Test system for LSI circuits resident on LSI chips |

| US4479088A (en) * | 1981-01-16 | 1984-10-23 | Burroughs Corporation | Wafer including test lead connected to ground for testing networks thereon |

| DE3138989A1 (de) * | 1981-09-30 | 1983-04-14 | Siemens AG, 1000 Berlin und 8000 München | Zusaetzliche funktionseinheit in einem mikroprozessor, mikroprozessorsystem und verfahren zu seinem betrieb |

| JPS5861639A (ja) * | 1981-10-08 | 1983-04-12 | Toshiba Corp | 半導体装置 |

| JPS58115828A (ja) * | 1981-12-29 | 1983-07-09 | Fujitsu Ltd | 半導体集積回路 |

| JPS609135A (ja) * | 1983-06-29 | 1985-01-18 | Fujitsu Ltd | Lsiの良品マツプの作成方法 |

| US4594711A (en) * | 1983-11-10 | 1986-06-10 | Texas Instruments Incorporated | Universal testing circuit and method |

| US4703436A (en) * | 1984-02-01 | 1987-10-27 | Inova Microelectronics Corporation | Wafer level integration technique |

| JPS6158254A (ja) * | 1984-08-29 | 1986-03-25 | Fujitsu Ltd | 半導体集積回路装置 |

| JPS61150228A (ja) * | 1984-12-24 | 1986-07-08 | Matsushita Electric Ind Co Ltd | Lsi検査回路 |

| US4635261A (en) * | 1985-06-26 | 1987-01-06 | Motorola, Inc. | On chip test system for configurable gate arrays |

-

1985

- 1985-07-24 DE DE19853526485 patent/DE3526485A1/de active Granted

-

1986

- 1986-06-20 IN IN461/CAL/86A patent/IN164539B/en unknown

- 1986-07-09 DE DE8686109401T patent/DE3681657D1/de not_active Expired - Lifetime

- 1986-07-09 AT AT86109401T patent/ATE67861T1/de not_active IP Right Cessation

- 1986-07-09 EP EP86109401A patent/EP0212208B1/de not_active Expired - Lifetime

- 1986-07-23 JP JP61171925A patent/JPS6316633A/ja active Pending

- 1986-07-24 CN CN86105604A patent/CN1011085B/zh not_active Expired

-

1988

- 1988-10-14 US US07/258,095 patent/US4961053A/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| ATE67861T1 (de) | 1991-10-15 |

| IN164539B (zh) | 1989-04-01 |

| EP0212208A1 (de) | 1987-03-04 |

| DE3526485A1 (de) | 1987-02-05 |

| JPS6316633A (ja) | 1988-01-23 |

| EP0212208B1 (de) | 1991-09-25 |

| CN86105604A (zh) | 1987-02-11 |

| DE3681657D1 (de) | 1991-10-31 |

| DE3526485C2 (zh) | 1987-08-06 |

| US4961053A (en) | 1990-10-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1011085B (zh) | 用于测试集成电路元件的电路结构 | |

| US5764655A (en) | Built in self test with memory | |

| KR950003012B1 (ko) | 반도체기억장치의용장회로 | |

| KR0135108B1 (ko) | 스트레스 테스트 회로를 포함하는 반도체 메모리 장치 | |

| US5289113A (en) | PROM for integrated circuit identification and testing | |

| US6897554B2 (en) | Test circuit and multi-chip package type semiconductor device having the test circuit | |

| US5818247A (en) | Method and apparatus for testing internal circuit | |

| US4860256A (en) | Integrated circuit provided with switching elements for changeover to redundancy elements in a memory | |

| KR20030074652A (ko) | 반도체 시험장치 | |

| US5712858A (en) | Test methodology for exceeding tester pin count for an asic device | |

| KR900015161A (ko) | 대규모 반도체 집적회로 장치와 그 결함구제 방법 | |

| CN108878306A (zh) | 一种多工位集成电路熔丝修调测试系统及其修调方法 | |

| US7227351B2 (en) | Apparatus and method for performing parallel test on integrated circuit devices | |

| CN1472700A (zh) | Ic卡芯片和模块芯片测试系统 | |

| EP1762855B1 (en) | JTAG port | |

| KR20030034012A (ko) | 테스트 어레이 및 어레이 테스트 방법 | |

| KR20050121376A (ko) | 반도체 장치의 테스트 장치 및 이를 이용한 반도체 장치테스트 방법 | |

| KR100279198B1 (ko) | 2개의 집적회로를 갖춘 플레이트 | |

| TW497243B (en) | Integrated circuit with a test driver and test facility for testing an integrated circuit | |

| US20030115519A1 (en) | Parallel testing system for semiconductor memory devices | |

| CN220040663U (zh) | 测试装置及测试机箱 | |

| KR20060029841A (ko) | 변형된 입출력용 인쇄회로패턴을 갖는 반도체 소자검사장치의 검사보오드 및 이를 이용한 검사방법 | |

| KR100568852B1 (ko) | 반도체 메모리 장치의 병렬 테스트 시스템 | |

| US6268718B1 (en) | Burn-in test device | |

| US6492706B1 (en) | Programmable pin flag |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C13 | Decision | ||

| GR02 | Examined patent application | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CX01 | Expiry of patent term |